S1D13521B01 Epson / E Ink Broadsheet

**Hardware Functional Specification**

No part of this material may be reproduced or duplicated in any form or by any means without the written permission of Seiko Epson. Seiko Epson reserves the right to make changes to this material without notice. Seiko Epson does not assume any liability of any kind arising out of any inaccuracies contained in this material or due to its application or use in any product or circuit and, further, there is no representation that this material is applicable to products requiring high level reliability, such as, medical products. Moreover, no license to any intellectual property rights is granted by implication or otherwise, and there is no representation or warranty that anything made in accordance with this material will be free from any patent or copyright infringement of a third party. This material or portions thereof may contain technology or the subject relating to strategic products under the control of the Foreign Exchange and Foreign Trade Law of Japan and may require an export license from the Ministry of International Trade and Industry or other approval from another government agency.

All other product names mentioned herein are trademarks and/or registered trademarks of their respective companies.

©SEIKO EPSON CORPORATION 2008, All rights reserved.

# **Table Of Contents**

| Chapte | r 1 Introduction                                           | . 9 |

|--------|------------------------------------------------------------|-----|

| 1.1    | Scope                                                      | .9  |

| 1.2    | Overview Description                                       | .9  |

| Chapte | r 2 Features                                               | 10  |

| 2.1    | Direct Source and Gate Driver for Electrophoretic Display  | 10  |

| 2.2    | 16-Bit Host Interface                                      | 10  |

| 2.3    | External Memory SDRAM Interface                            | 10  |

| 2.4    | Power Management IC Support                                |     |

| 2.5    | Image Buffer Flexibility                                   | 10  |

| 2.6    | I2C Thermal Sensor Temperature Reading                     | 11  |

| 2.7    | Serial Flash Memory Waveform Read                          | 11  |

| 2.8    | Clock Source                                               | 11  |

| 2.9    | Miscellaneous                                              | 11  |

| Chapte | r 3 Block Diagram                                          | 12  |

| 3.1    | Typical System Implementation                              | 13  |

| Chapte | r 4 Pins                                                   | 14  |

| 4.1    | Pinout Diagram                                             |     |

| 4.2    | Pin Descriptions                                           |     |

| 2      | 4.2.1 Shared Host Interface                                |     |

| 2      | 4.2.2 Host Interface                                       | 17  |

| 4      | 4.2.3 SDRAM Interface                                      |     |

| 2      | 4.2.4 SPI Master Interface for Serial Flash                | 19  |

| 2      | 4.2.5 I2C Master Interface for Thermal Sensor              | 19  |

| 2      | 4.2.6 Gate Driver Interface                                | 19  |

| 2      | 4.2.7 Sourc <mark>e</mark> Driver I <mark>nt</mark> erface | 20  |

| 4      | 4.2.8 Power Switches Control Interface                     | 21  |

| 4      | 4.2.9 Display Border Power Interface                       | 21  |

| 4      | 4.2.10 Miscellaneous                                       | 22  |

| 4      | 4.2.11 Power and Ground                                    | 23  |

| 4.3    | Configuration Pins                                         | 24  |

| 4.4    | Pin Mapping                                                | 25  |

| 4      | 4.4.1 Source Driver Interface                              | 25  |

| 4      | 4.4.2 Border Pin Interface                                 | 25  |

| Chapte | r 5 D.C. Characteristics                                   | 26  |

| 5.1    | Absolute Maximum Ratings                                   | 26  |

| 5.2    | Recommended Operating Conditions                           | 26  |

| 5.3 Electrical Characteristics                   | .27  |

|--------------------------------------------------|------|

| Chapter 6 A.C. Characteristics                   | .29  |

| 6.1 Clock Timing                                 | .30  |

| 6.1.1 Input Clocks                               | . 30 |

| 6.1.2 PLL Clock                                  | . 31 |

| 6.2 Power Supply Sequence                        | .32  |

| 6.2.1 Power-On Sequence                          | . 32 |

| 6.2.2 Power-Off Sequence                         | . 32 |

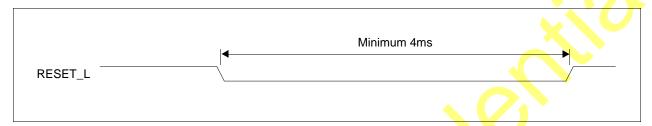

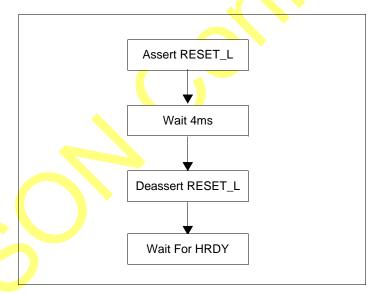

| 6.3 RESET_L Timing                               | .33  |

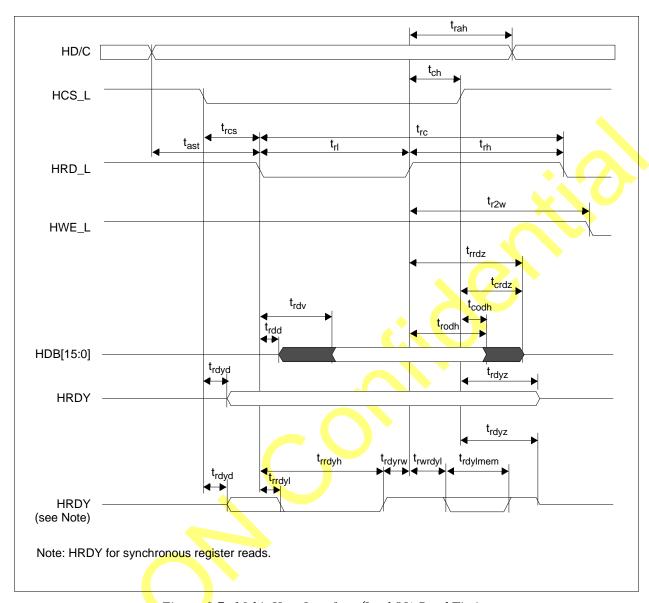

| 6.4 Host Interface Timing                        | .34  |

| 6.4.1 16-bit Host Interface Timing (Intel 80)    |      |

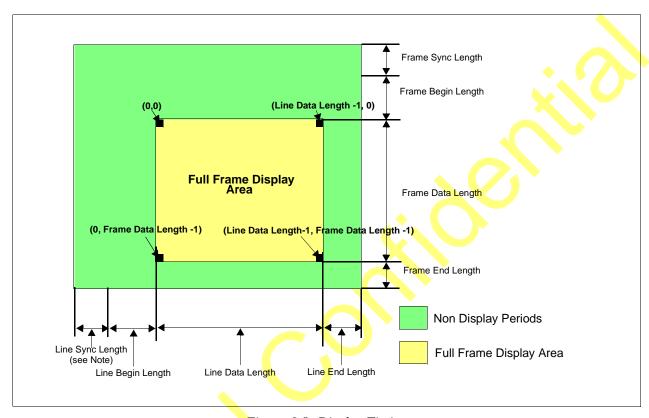

| 6.5 Display Timings                              |      |

| 6.5.1 Frame Rate Calculation Guide               |      |

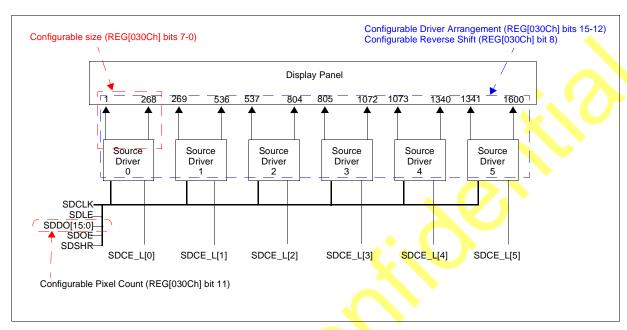

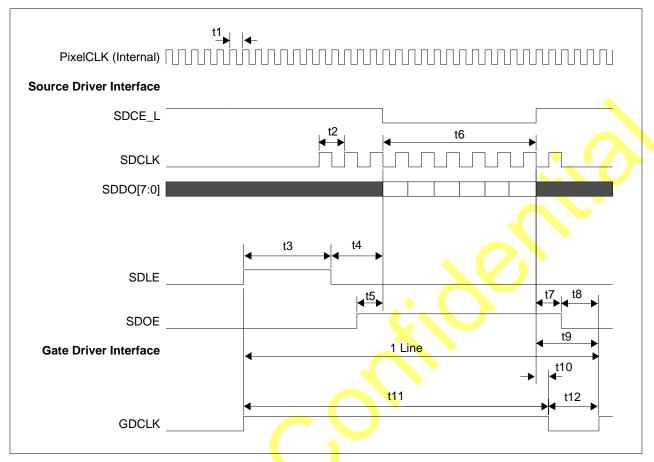

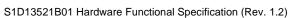

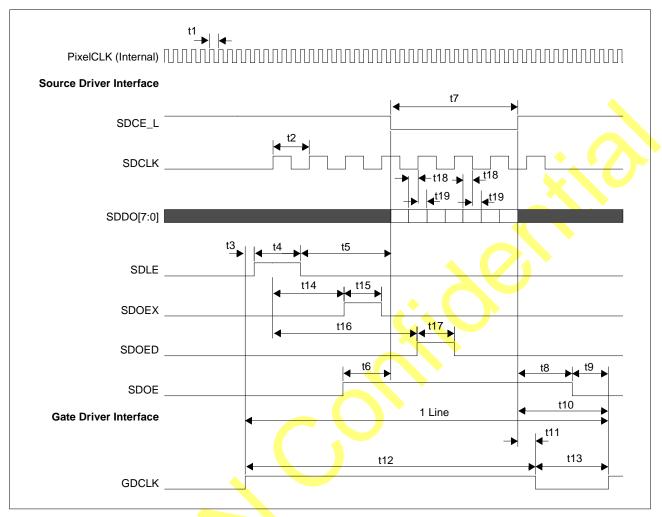

| 6.5.2 Interpreted Source Driver Timings          |      |

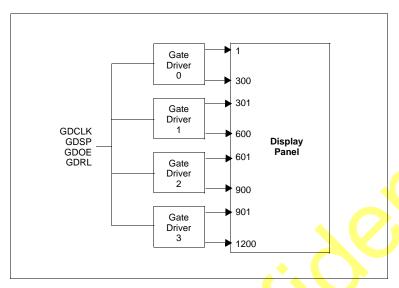

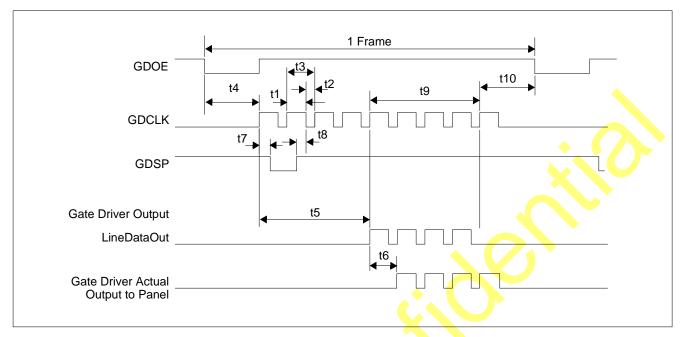

| 6.5.3 Interpreted Gate Driver Timings            |      |

| 6.6 Power Pin Interface                          |      |

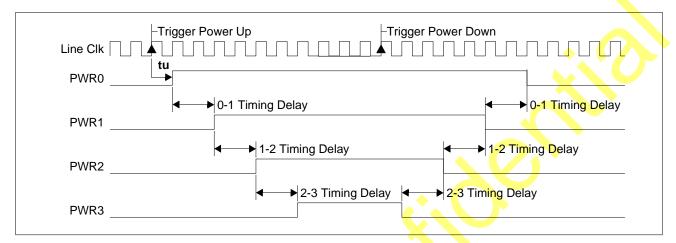

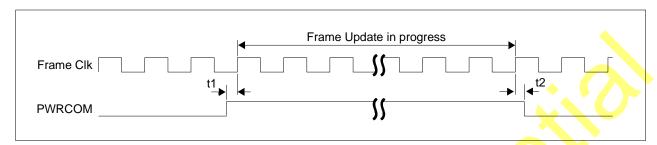

| 6.6.1 Power Pin Transition Sequence for PWR[3:0] |      |

| 6.6.2 Power Pin Transition Sequence for PWRCOM   | . 49 |

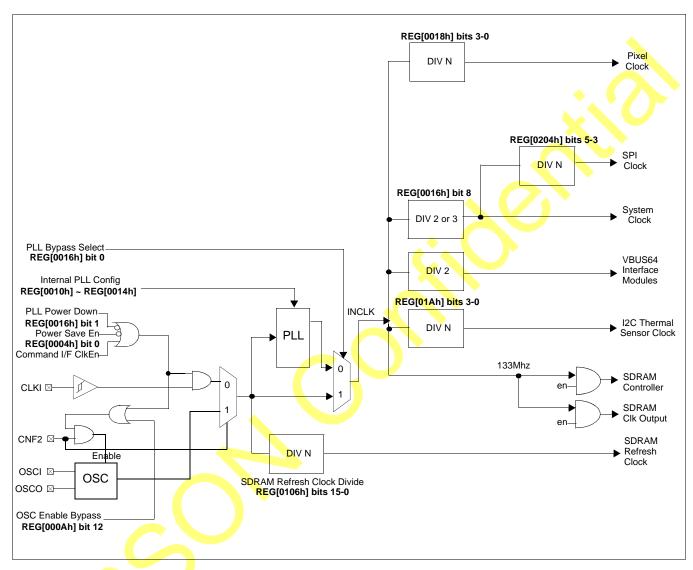

| Chapter 7 Clocks                                 | .50  |

| 7.1 Clock Descriptions                           | .50  |

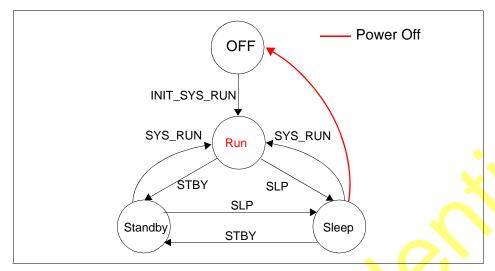

| Chapter 8 Power Management                       | .51  |

| 8.1 Power Management State Description           |      |

| Chapter 9 Host Interface                         | .54  |

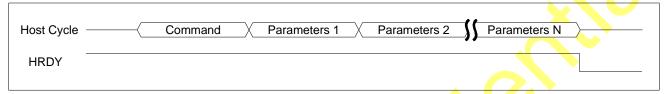

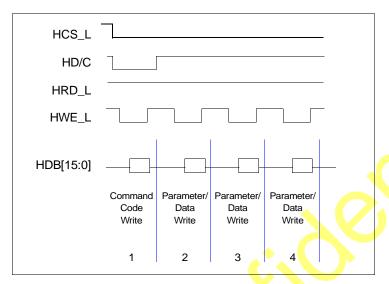

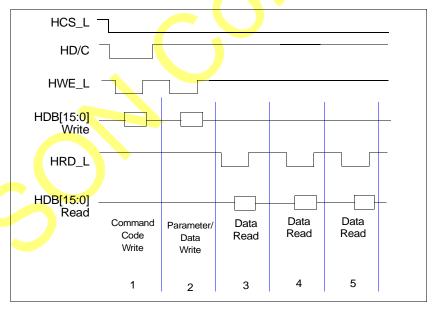

| 9.1 Host Cycle Sequences                         |      |

| 9.1.1 Command and Parameter Cycle                |      |

| 9.1.2 Memory Access Combination Cycle            |      |

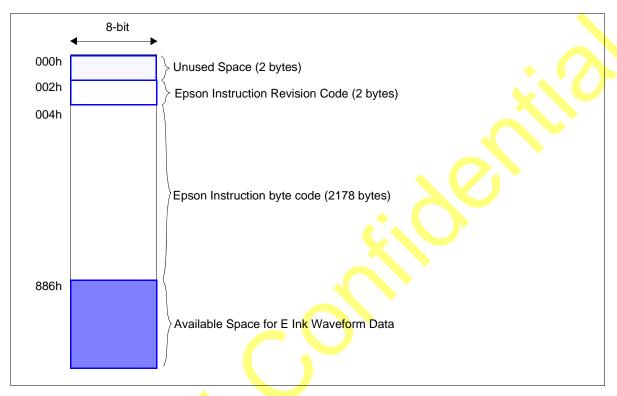

| 9.2 Serial Flash Memory Contents                 | .55  |

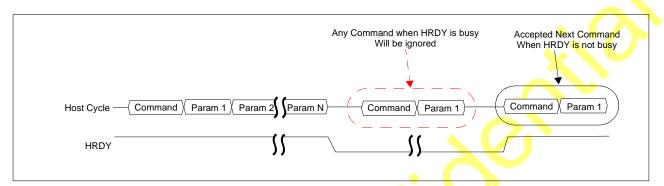

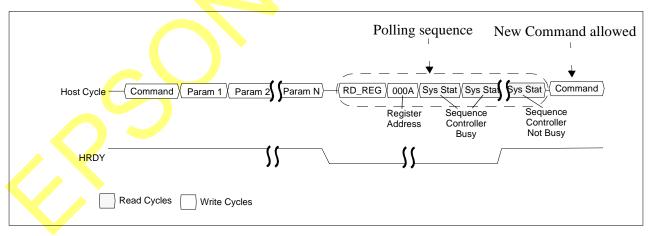

| 9.3 HRDY (Wait Line) Usage                       | .56  |

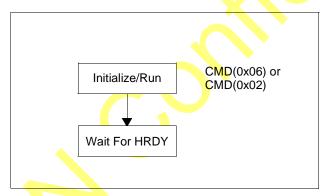

| 9.4 Command Operation                            | .57  |

| 9.5 Command List                                 | .58  |

| 9.6 Host Interface Command Descriptions          | .60  |

| 9.6.1 INIT_CMD_SET (0x00 + 3 parameters)         | . 61 |

| 9.6.2 INIT_PLL_STBY (0x01 + 3 parameters)        | . 62 |

| 9.6.3 RUN_SYS (0x02 + 0 parameters)              | . 62 |

| 9.6.4 STBY (0x04 + 0 parameters)                 | . 63 |

| 9.6.5 SLP (0x05 + 0 parameters)                  | . 63 |

| 9.6.6 INIT_SYS_RUN (0x06 + 0 parameters)         | . 63 |

| 9.6.7 INIT_SYS_STBY (0x07 + 0 parameters)        | . 64 |

| 9.6.8 INIT_SDRAM (0x08 + 4 parameters)           | . 64 |

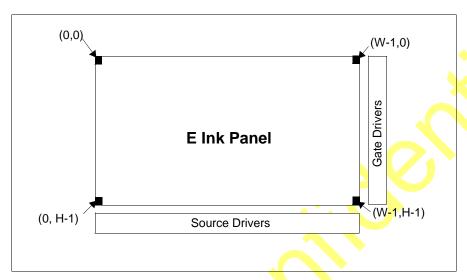

| 9.6.9                    | INIT_DSPE_CFG (0x09 + 5 parameters)                                             | 65 |

|--------------------------|---------------------------------------------------------------------------------|----|

| 9.6.10                   | INIT_DSPE_TMG (0x0A + 5 parameters)                                             | 67 |

| 9.6.11                   | INIT_ROTMODE (0x0B + 1 parameter)                                               | 68 |

| 9.6.12                   | RD_REG (0x10 + 2 parameters)                                                    | 58 |

| 9.6.13                   | WR_REG (0x11 + 2 parameters)                                                    | 58 |

| 9.6.14                   | RD_SFM (0x12 + 0 parameters)                                                    | 58 |

| 9.6.15                   | WR_SFM (0x13 + 1 parameter)                                                     | 59 |

| 9.6.16                   | END_SFM (0x14 + 0 parameters)                                                   | 59 |

| 9.6.17                   | BST_RD_SDR (0x1C + 4 parameters)                                                | 59 |

| 9.6.18                   | BST_WR_SDR (0x1D + 4 parameters)                                                | 70 |

| 9.6.19                   | BST_END_SDR (0x1E + 0 parameters)                                               | 71 |

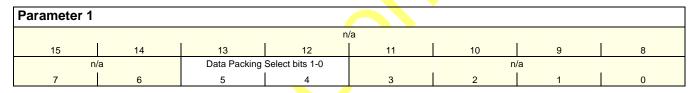

| 9.6.20                   | LD_IMG (0x20 + 1 parameter)                                                     | 71 |

| 9.6.21                   | LD_IMG_AREA (0x22 + 5 parameters)                                               | 72 |

| 9.6.22                   | $LD_IMG_END$ (0x23 + 0 parameters)                                              | 73 |

| 9.6.23                   | LD_IMG_WAIT $(0x24 + 0 \text{ parameters})$                                     | 73 |

| 9.6.24                   | LD_IMG_SETADR (0x25 + 2 parameters)                                             | 73 |

| 9.6.25                   | LD_IMG_DSPEADR $(0x26 + 0 \text{ parameters})$                                  | 74 |

| 9.6.26                   | WAIT_DSPE_TRG (0x28 + 0 parameters)                                             | 74 |

| 9.6.27                   | WAIT_DSPE_FREND (0x29 + 0 parameters)                                           | 74 |

| 9.6.28                   | WAIT_DSPE_LUTFREE (0x2A + 0 parameters)                                         | 74 |

| 9.6.29                   | WAIT_DSPE_MLUTFREE (0x2B + 1 parameter)                                         | 74 |

| 9.6.30                   | RD_WFM_INFO $(0x30 + 2 \text{ parameters})$                                     | 75 |

| 9.6.31                   | UPD_INIT $(0x32 + 0 \text{ parameters})$                                        | 75 |

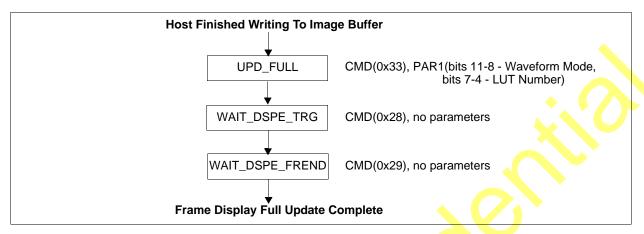

| 9.6.32                   | UPD_FULL (0x33 + 1 parameter)                                                   | 75 |

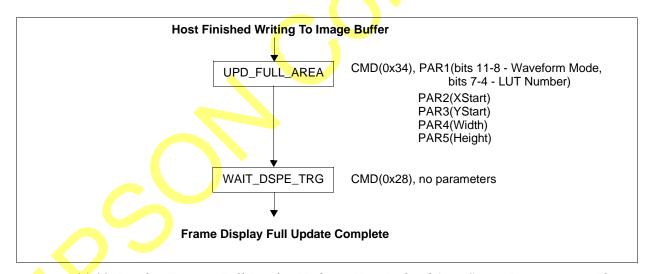

| 9.6.33                   | UPD_FULL_AREA (0x34 + 5 parameters)                                             | 76 |

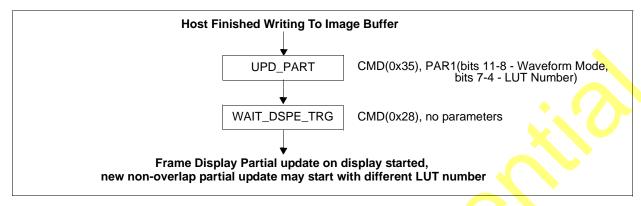

| 9.6.34                   | UPD_PART ( $0x35 + 1$ parameter)                                                | 77 |

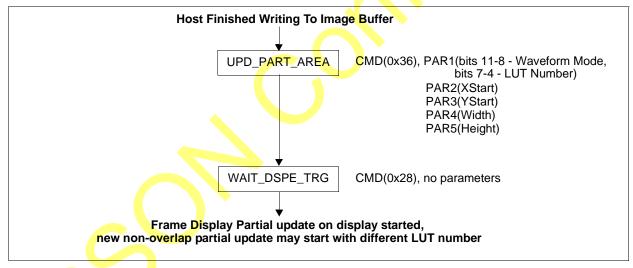

| 9.6.35                   | UPD_PART_AREA (0x36 + 5 parameters)                                             | 77 |

| 9.6.36                   | UPD_GDRV_CLR (0x37 + 0 parameters)                                              | 78 |

| 9.6.37                   | UPD_SET_IMGADR (0x38 + 2 parameters)                                            | 78 |

| Chapter 10 D             | isplay <mark>M</mark> emory Configurations .................................... | 79 |

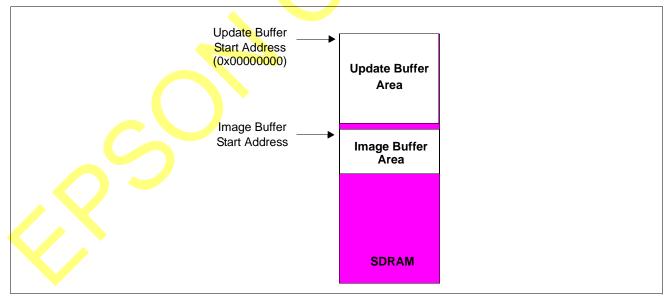

| 10.1 Introd              | duction                                                                         | 79 |

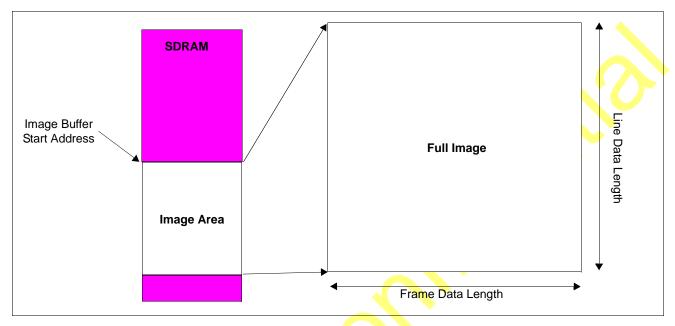

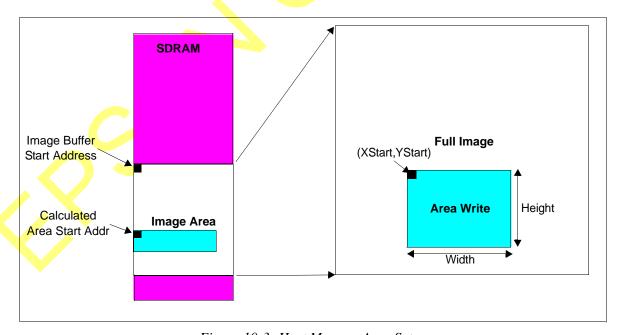

| 1 <mark>0.2 Ima</mark> g | e Buffer Memory Area Setup                                                      | 30 |

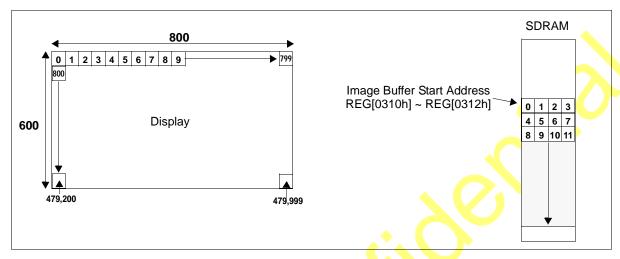

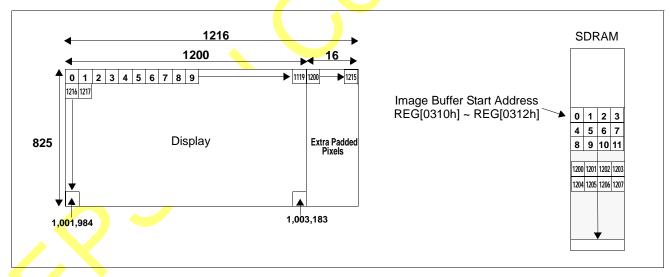

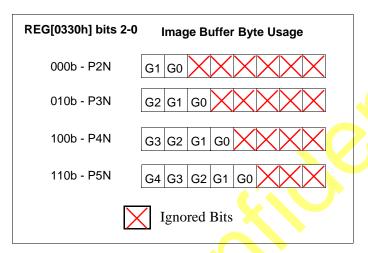

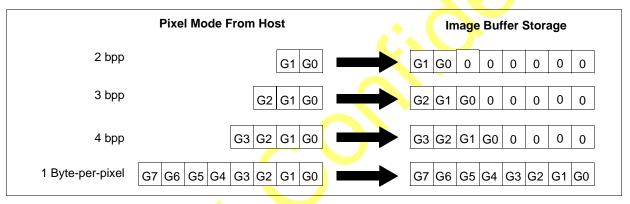

| 10.2.1                   | Image Buffer Storage                                                            | 81 |

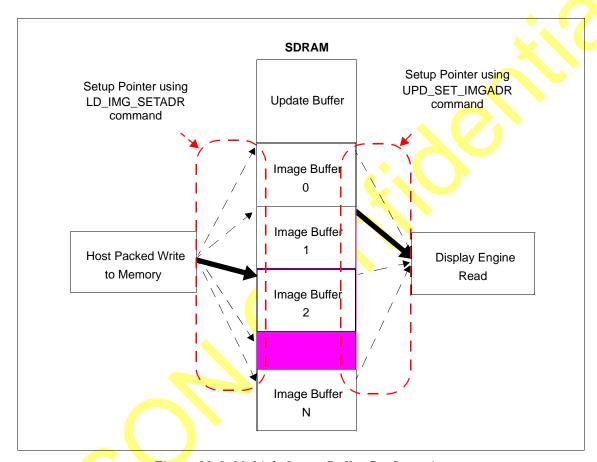

| 10.2.2                   | Multiple Image Buffer Support                                                   | 82 |

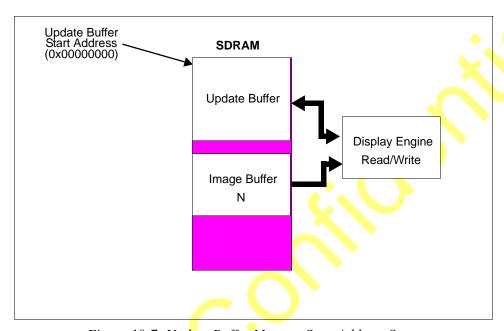

| 10.3 Upda                | te Buffer Memory Area Setup                                                     | 83 |

| 10.3.1                   | Update Buffer Usage                                                             | 84 |

| 10.4 Displ               | ay Engine Usage of the Image Buffer                                             | 35 |

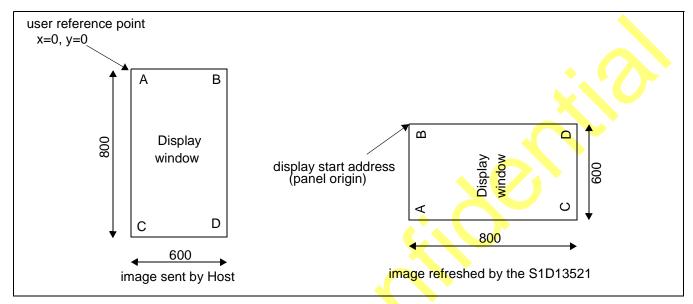

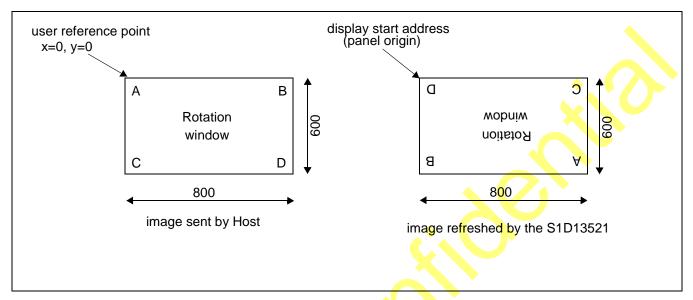

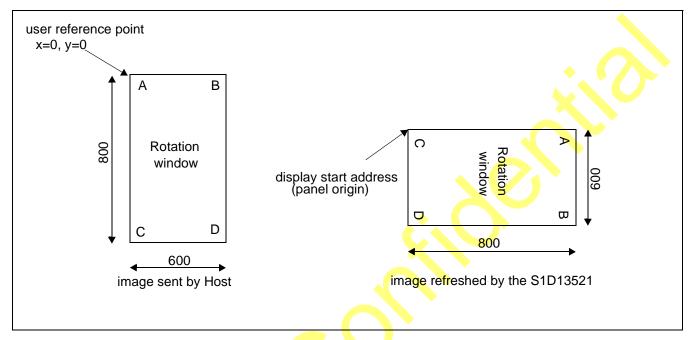

| 10.5 Rotat               | ion Support                                                                     | 86 |

| 10.5.1                   | Rotation Introduction                                                           | 86 |

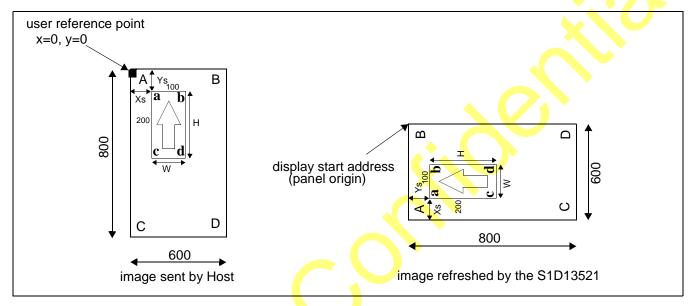

| 10.5.2                   | 90° Rotation                                                                    | 87 |

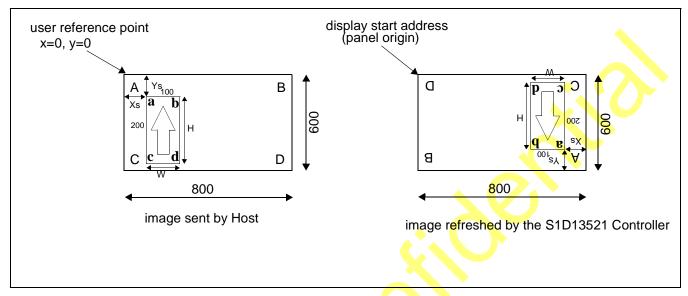

| 10.5.3 180° Rotation                                                           | 88         |

|--------------------------------------------------------------------------------|------------|

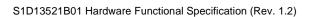

| 10.5.4 270° Rotation                                                           | 89         |

| 10.6 Window Area Position / Rotation                                           | 90         |

| 10.6.1 90° Rotation                                                            | 90         |

| 10.6.2 180° Rotation                                                           | 91         |

| 10.6.3 270° Rotation                                                           | 92         |

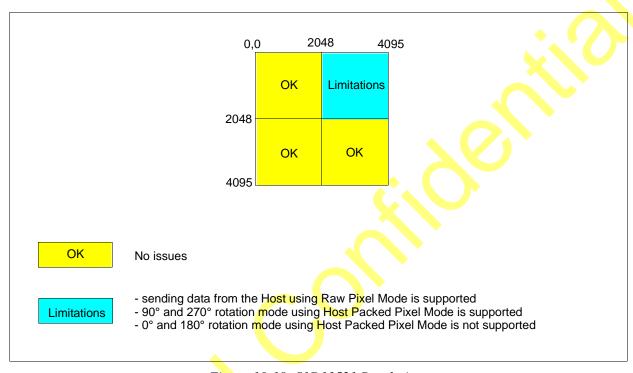

| 10.7 Resolution Support                                                        | 93         |

| Chapter 11 Host Memory Transfer Format                                         | 94         |

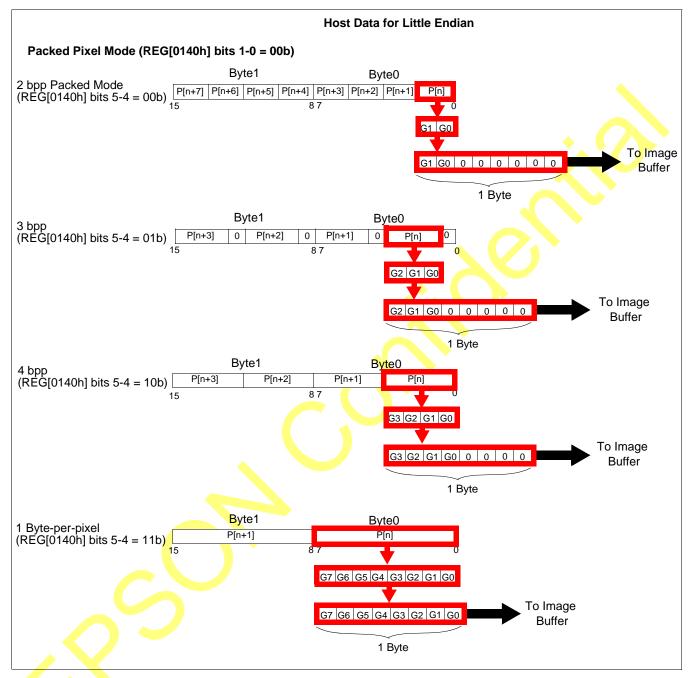

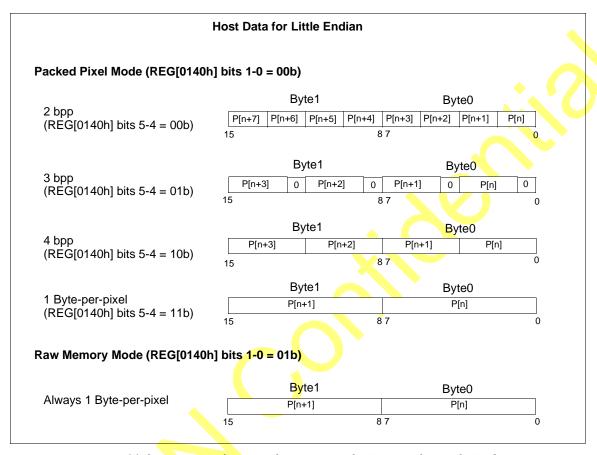

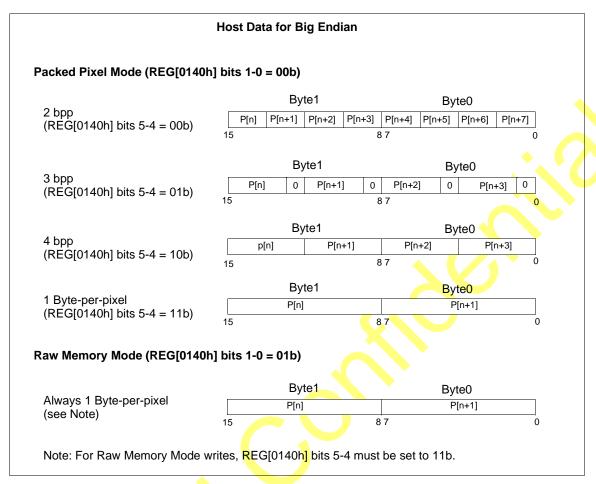

| 11.1 Host Interface Memory Transfer Mode                                       | 94         |

| 11.1.1 Display Engine LUT Format and Host Interface Packed Pixel Mode Compatib | ility . 96 |

| 11.2 Host Interface Packed Pixel Data Transfer Format Endian Formatting        | 97         |

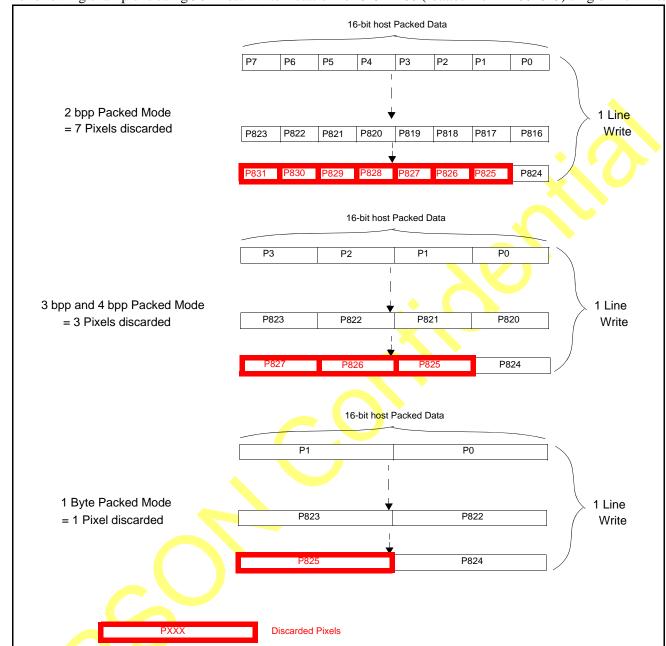

| 11.2.1 Packed Pixel Handling of Odd Display Widths for 90/270° Rotation        | 98         |

| 11.2.2 Packed Pixel Area Size Transfer Limitations                             | 100        |

| Chapter 12 Display Operations                                                  | 101        |

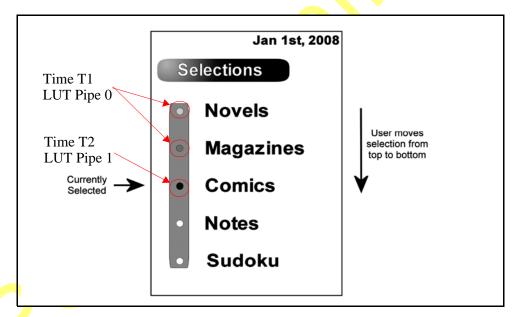

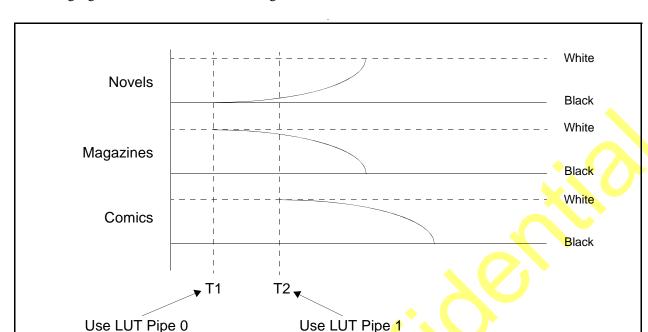

| 12.1 Display Update: Multi-Region LUT Pipeline Usage                           |            |

| 12.1.1 User Interface Applications with Multi-Region LUT Pipeline              |            |

| 12.1.2 Display Update Commands                                                 |            |

| 12.1.3 Managing LUT Pipeline Usage                                             |            |

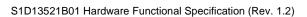

| 12.2 Guaranteed Display Update Operation Flow                                  |            |

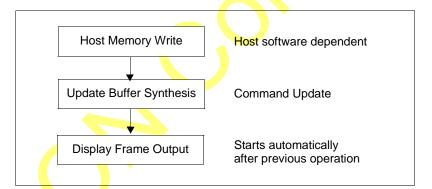

| 12.3 Guaranteed Host Memory Write Display Trigger Operation Timing             |            |

| 12.3.1 Guaranteed Display Update Operation Analysis                            | 106        |

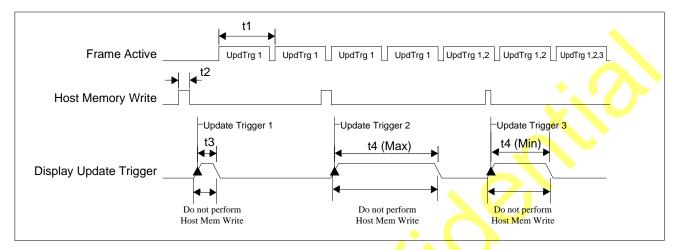

| 12.4 Asynchronous Host Memory Write Display Trigger Operation Timing           |            |

| 12.4.1 Asynchronous Display Update Operation Analysis                          | 107        |

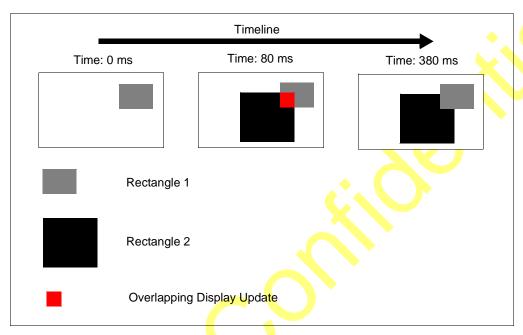

| 12.5 Overlapping Display Update Operation Flow                                 | 108        |

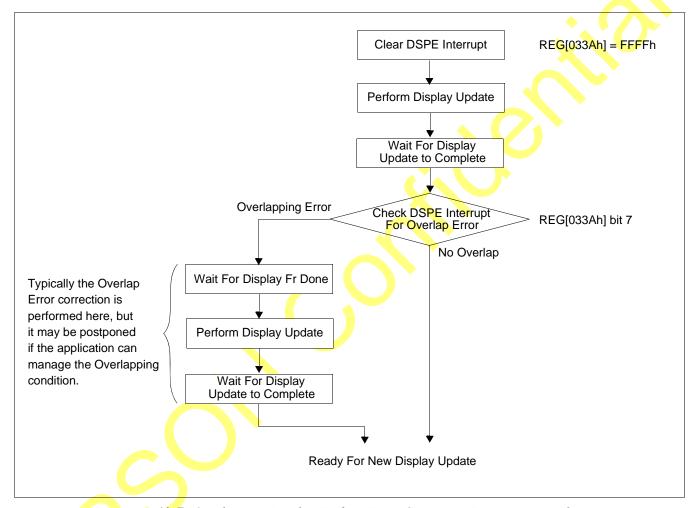

| 12.5.1 Overlapping Display Updates                                             | 108        |

| 12.5.2 Overlapping Display Update Recommended Programming Flow                 | 109        |

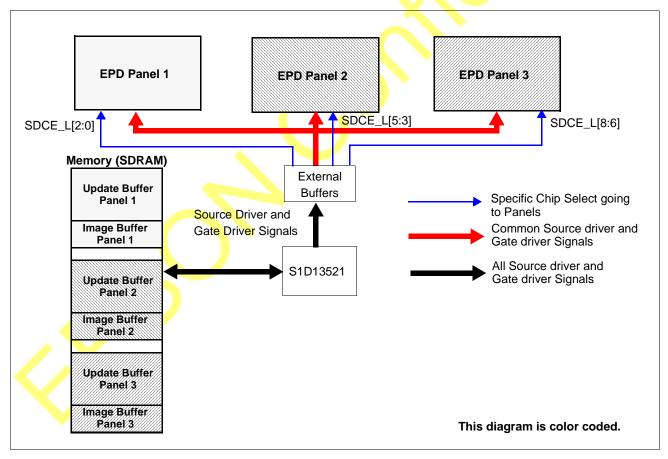

| 12.6 Multi-Panel Support                                                       | 110        |

| 12.6.1 Source and Gate Driver Output Connections                               | 110        |

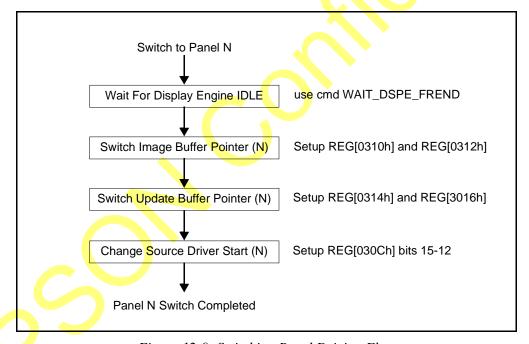

| 12.6.2 Configuration of Source Driver Chip Selects                             | 111        |

| 12.6.3 Switching Between Panels                                                | 111        |

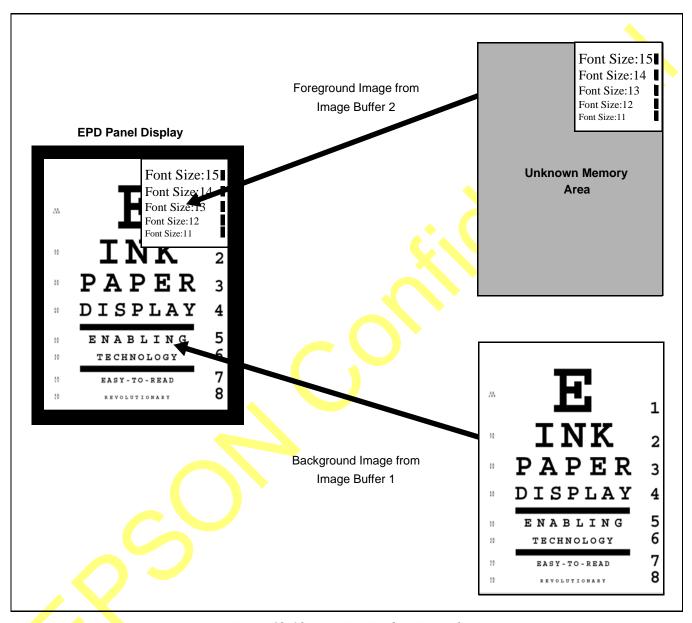

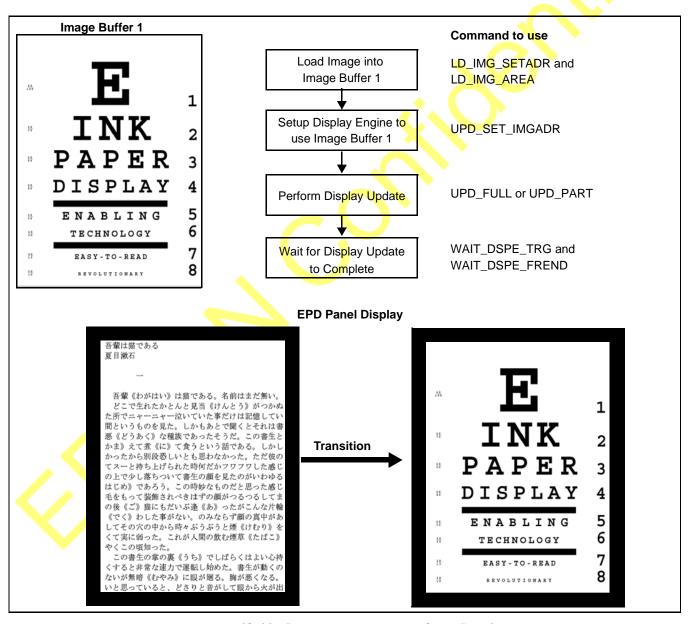

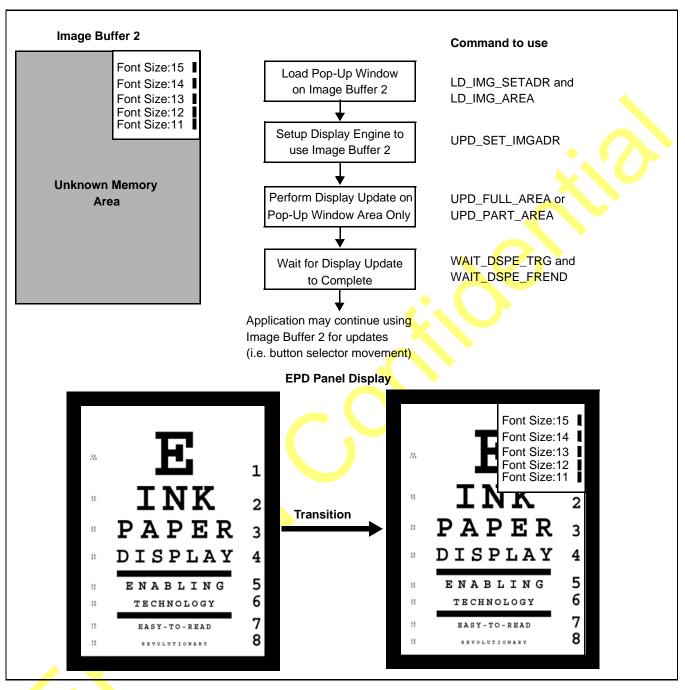

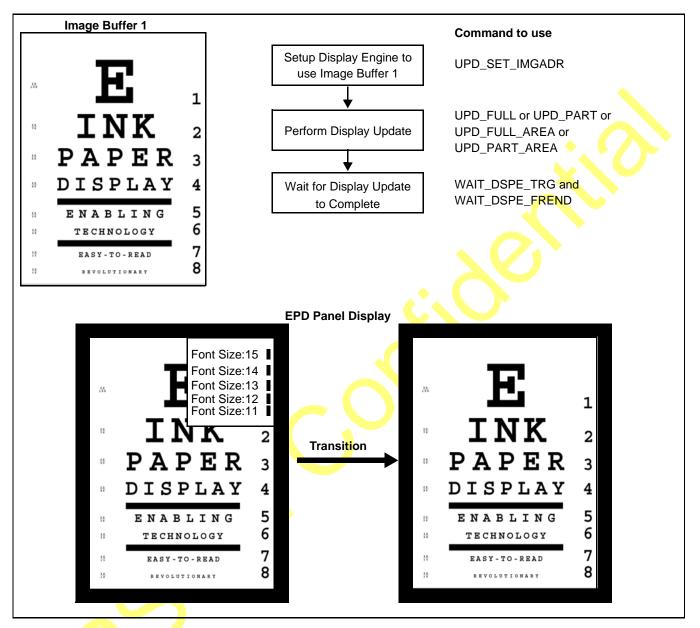

| 12.7 Pop-Up Window Support                                                     | 112        |

| 12.7.1 Pop-Up Window Implementation                                            | 113        |

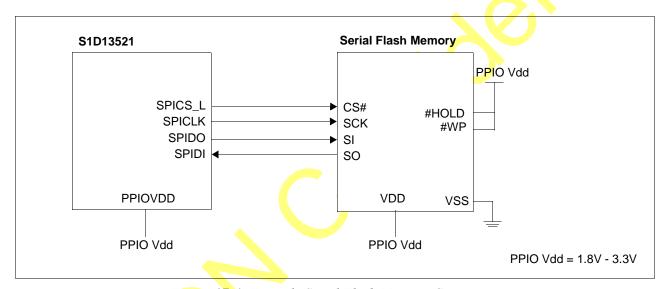

| Chapter 13 SPI Interface                                                       | 116        |

| 13.1 Register Descriptions                                                     | 116        |

| 13.1.1 SPI Flash Chip Select Control Register                                  | 116        |

| 13.1.2 SPI Flash Control Register                                              | 116        |

| 13.1.3 SPI Flash Write Data Register                                           | 116        |

| 13.1.4 SPI Flash Read Data Register                                            | 116        |

| 13.1.5 SPI Flash Status Register                                               | 117        |

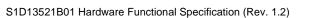

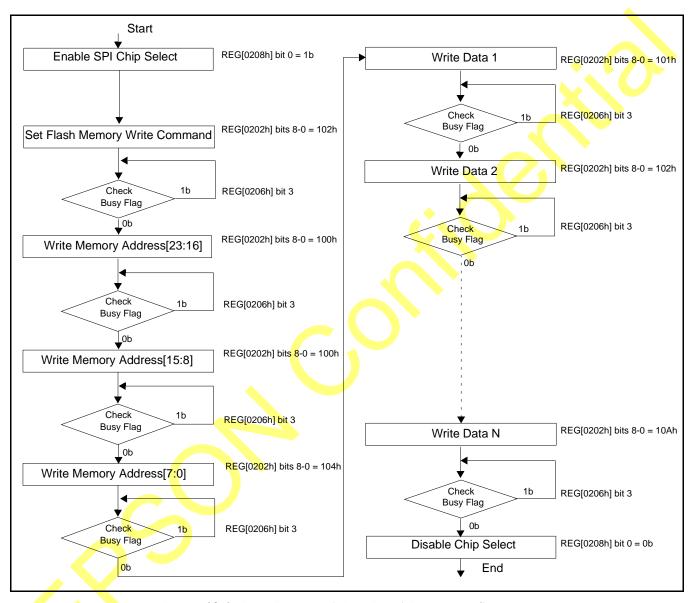

| 13.2 Flash Memory Accesses using SPI Interface Registers                       | 118        |

| Chapter 14 Firmware Programming Guide                                     | 120 |

|---------------------------------------------------------------------------|-----|

| 14.1 Command Based Programming                                            | 120 |

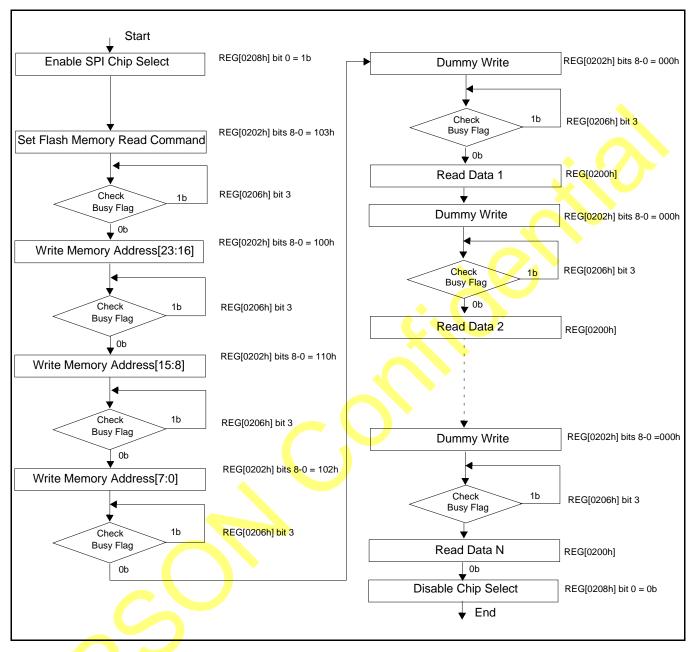

| 14.1.1 Initializing and Programming a Blank Serial Flash                  | 121 |

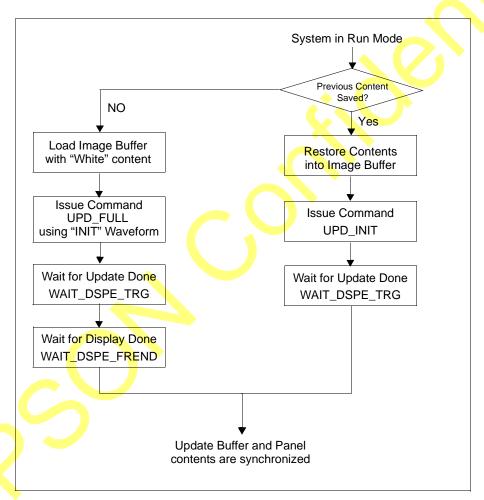

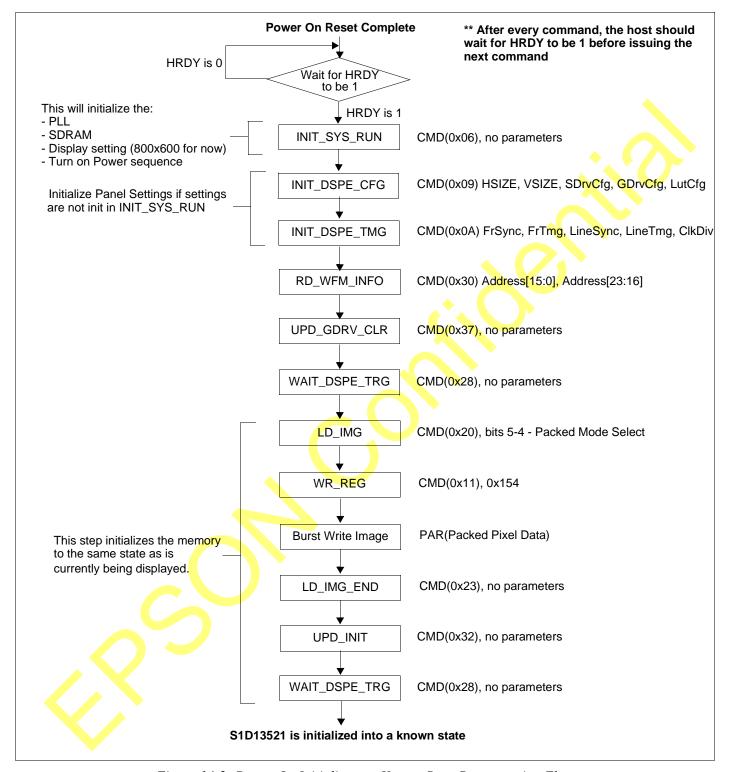

| 14.1.2 Power On Initialize to a Known State (Stored Image)                | 122 |

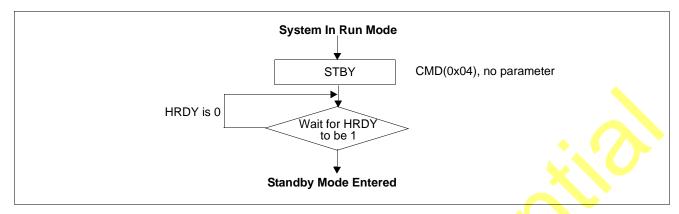

| 14.1.3 Standby Mode                                                       | 123 |

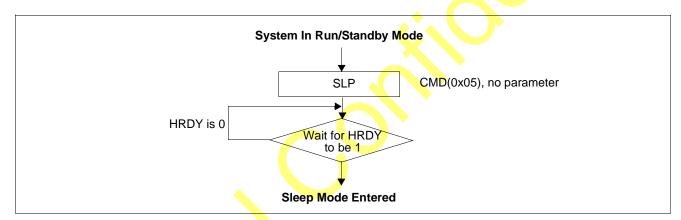

| 14.1.4 Sleep Mode                                                         | 123 |

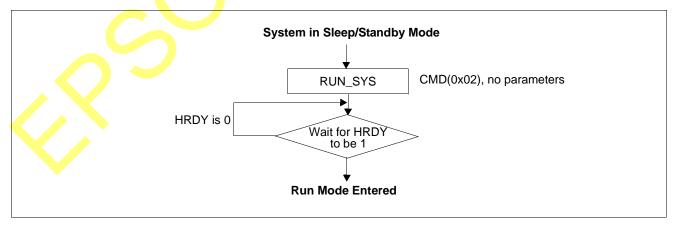

| 14.1.5 Run Mode                                                           |     |

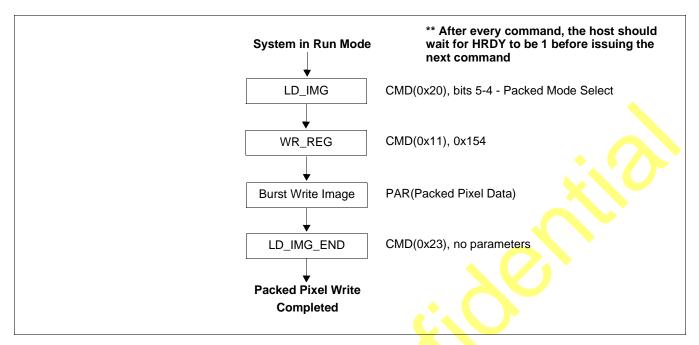

| 14.1.6 Host Packed Pixel Write                                            | 124 |

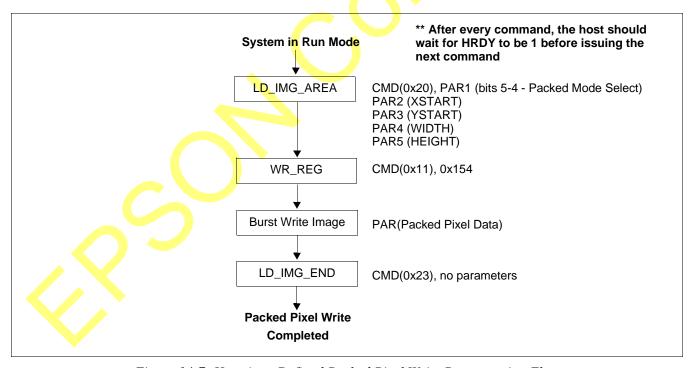

| 14.1.7 Host Area Defined Packed Pixel Write                               |     |

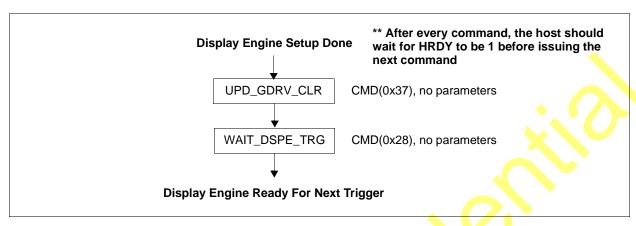

| 14.1.8 Display Engine - Gate Driver Clear Request                         |     |

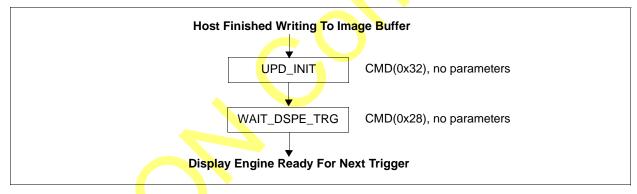

| 14.1.9 Display Engine - Update Buffer Initialize with Image Buffer        | 125 |

| 14.1.10 Display Engine - Full Display Update - Full Image Size Sweep      | 126 |

| 14.1.11 Display Engine - Full Display Update - User Defined Area Sweep    |     |

| 14.1.12 Display Engine - Partial Display Update - Full Image Size Sweep   |     |

| 14.1.13 Display Engine - Partial Display Update - User Defined Area Sweep | 127 |

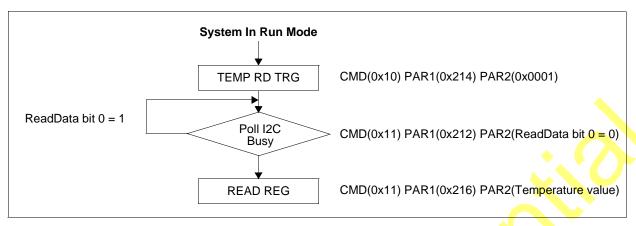

| 14.1.14 Manual Trigger to I2C Thermal Sensor for Single Temperature Read  |     |

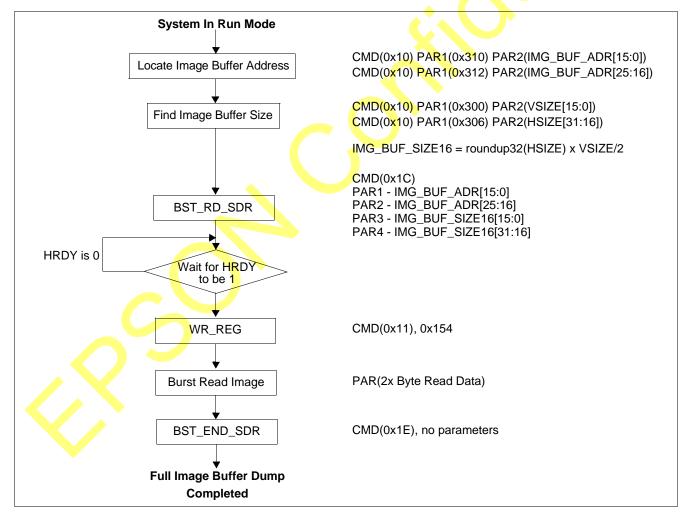

| 14.1.15 Full Image Buffer Dump (Byte Data Only) ,                         | 128 |

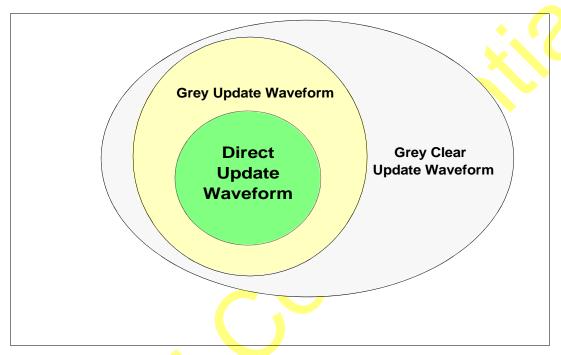

| Chapter 15 Auto Waveform Mode                                             | 129 |

| 15.1 Introduction                                                         | 129 |

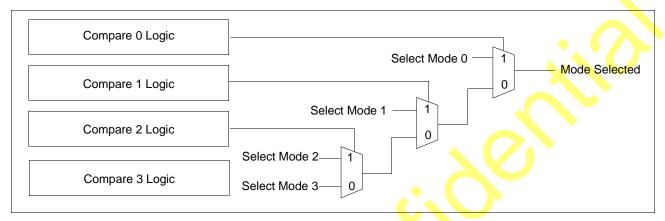

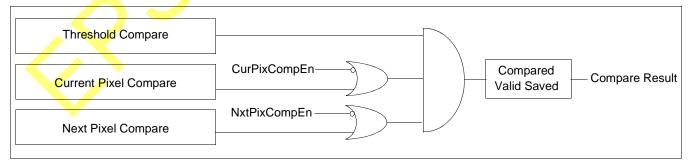

| 15.2 Architecture                                                         | 130 |

| 15.3 Auto Waveform Mode Example Setup                                     | 131 |

| Chapter 16 Waveform Modes                                                 | 132 |

| Chapter 17 External Components                                            | 133 |

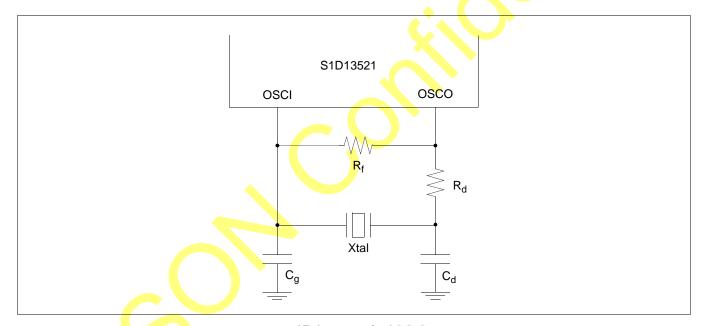

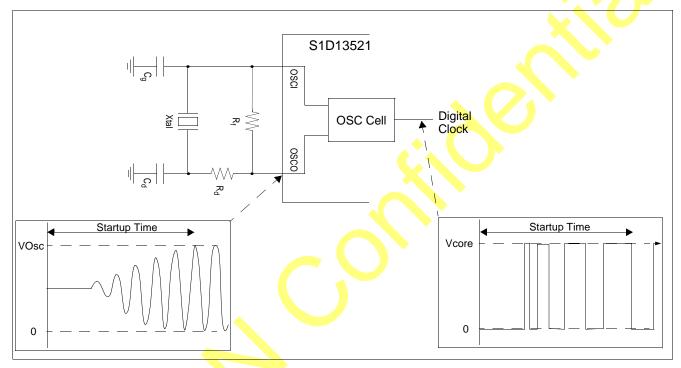

| 17.1 OSC Circuit                                                          | 133 |

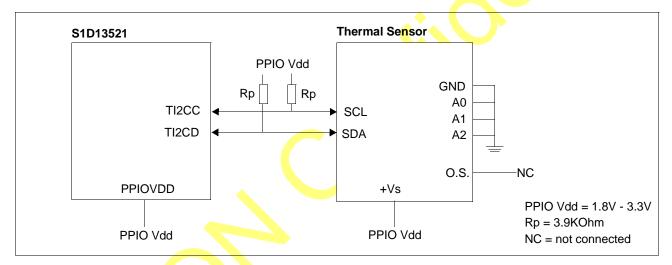

| 17.2 LM75 Compatible Thermal Sensor                                       | 134 |

| 17.2.1 Thermal Sensor Connection Example                                  | 134 |

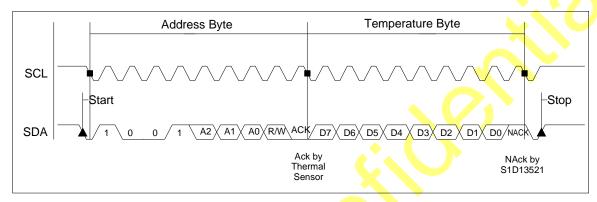

| 17.2.2 Thermal Sensor Operation Timing                                    | 135 |

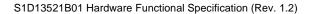

| 17.3 Serial Flash Memory                                                  | 136 |

| 17.3.1 Serial Flash Memory Connection Example                             | 136 |

| 17.3.2 Serial Flash Memory Operation Timing                               | 137 |

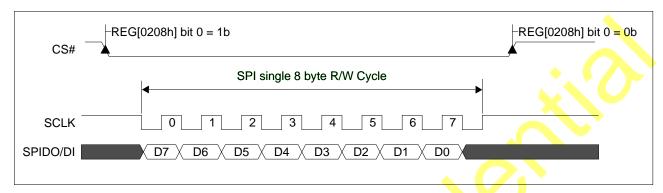

| 17.4 SDRAM                                                                | 138 |

| 17.4.1 SDRAM Size Requirements                                            | 138 |

| 17.4.2 SDRAM Connection Example                                           | 139 |

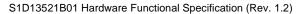

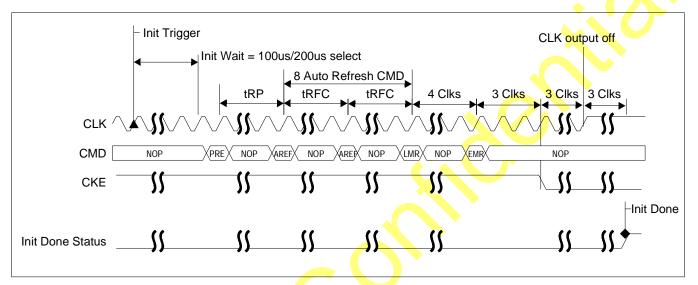

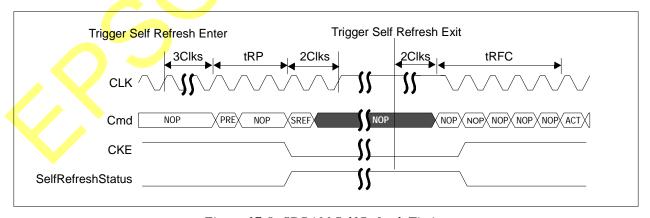

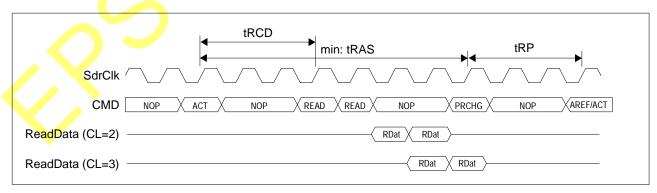

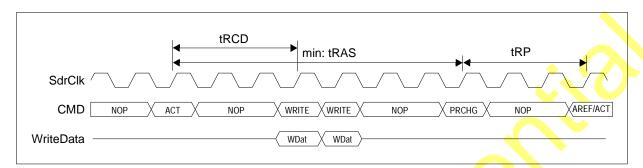

| 17.4.3 SDRAM Operation Timing                                             |     |

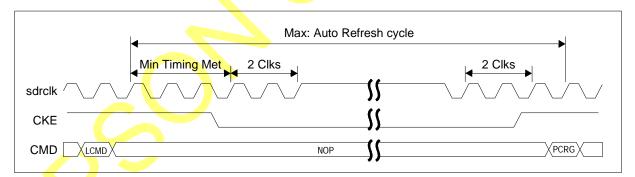

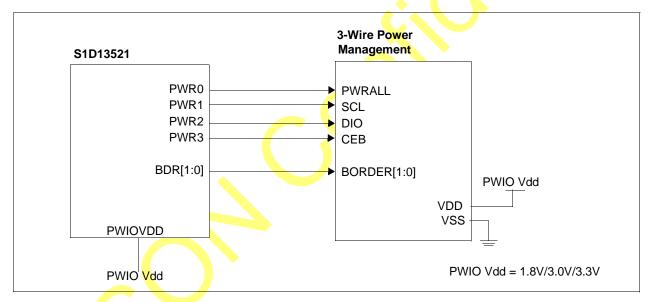

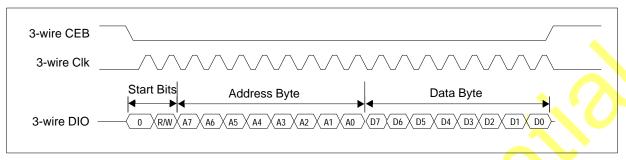

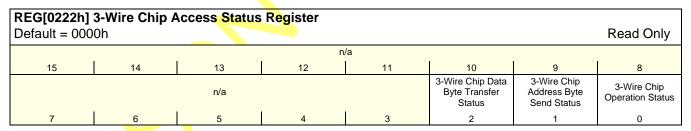

| 17.5 3-Wire Power Management                                              | 143 |

| 17.5.1 3-Wire Power Management Connection Example                         | 143 |

| 17.5.2 3-Wire Power Management Operation Timing                           | 144 |

| Chapter 18 OSC Clock Timing Requirements                                  | 145 |

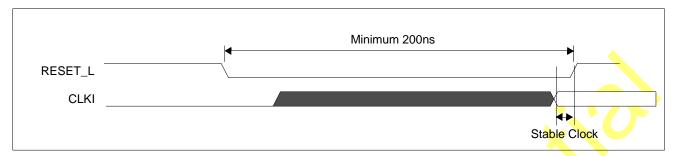

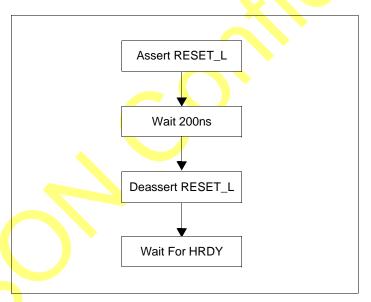

| 18.1 Timing Requirements For Reset                                        | 146 |

| 18.1.1 Input Clock From OSCI/OSCO                                         | 146 |

# **Chapter 1 Introduction**

## 1.1 Scope

This is the Hardware Functional Specification for the S1D13521B01 EPD Controller. Included in this document are timing diagrams, AC and DC characteristics, register descriptions, and power management descriptions. This document is intended for two audiences: Display Subsystem Designers and Software Developers.

This document is updated as appropriate. Please check for the latest revision of this document before beginning any development. The latest revision can be downloaded at www.erd.epson.com.

We appreciate your comments on our documentation. Please contact us via email at documentation@erd.epson.com.

## 1.2 Overview Description

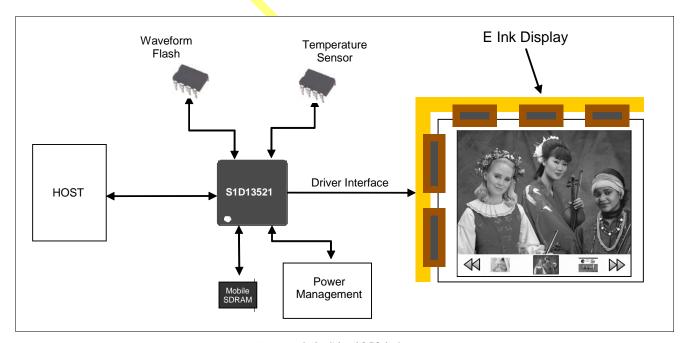

EPSON's S1D13521 controller provides a high performance, low cost, solution for current and future E Ink EPDs (Electronic Paper Displays). The controller greatly reduces CPU overhead by providing many functions that were previously handled by the Host.

S1D13521 allows multi-regional and concurrent display updates resulting in highly responsive screen changes. This increased responsiveness finally makes touch pen support and on-screen user interfaces viable, opening up a range of new applications.

Additionally, the S1D13521 integrates support for current and future power management chips, as well as future 16 and 32 gray level waveforms. All this is achieved with a lower parts cost than previous EPD controllers making the S1D13521 a perfect choice for new designs and design upgrades.

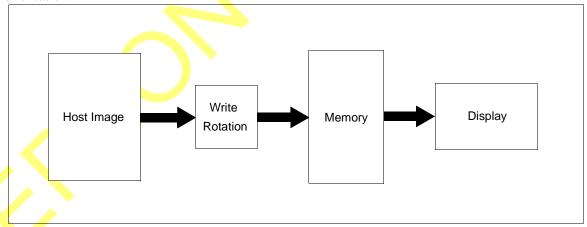

Figure 1-1: S1D13521 Overview

# **Chapter 2 Features**

## 2.1 Direct Source and Gate Driver for Electrophoretic Display

- Supports up to 2048x1536 resolution @ 50Hz

- Supports up to 4096x4096 resolution @ less than 50Hz (see 10.7, "Resolution Support" on page 93)

- Up to 5-bit grayscale waveforms (2 / 3 / 4 / 5 bpp)

- Source Driver interfaces to the Micronix MX860 IC and compatible devices

- Programmable up to 1024 pixels per IC

- Gate Driver interfaces to the Sharp LH1692 and compatible devices

- Panel Border Support

#### 2.2 16-Bit Host Interface

- Indirect 16-bit Host Bus Interface (Intel 80)

- Registers can be accessed using Command Mode

- User programmed commands can be used to execute a pre-programmed series of commands

- DMA compatible memory bus style host interface

## 2.3 External Memory SDRAM Interface

- 16/32-bit mobile SDRAM Interface

- Programmable Column Addressing Width

- Maximum operating frequency: 133MHz

## 2.4 Power Manag<mark>e</mark>ment I<mark>C</mark> Support

• Supports 3-wire Active Matrix Power Management ICs

## 2.5 Image Buffer Flexibility

- Host Writes can be rotated counter-clockwise by 90°, 180°, or 270°

- Host Write data input can use packed mode for high-speed transfers

- New image data can be loaded to the image buffer while display updates are in progress

## 2.6 I2C Thermal Sensor Temperature Reading

- Supports I2C sequence for temperature reading

- Supports National LM75 Digital Temperature Sensor and compatible devices

## 2.7 Serial Flash Memory Waveform Read

- Serial Flash Memory for Waveform Reads

- High Speed SPI Mode (the Fast Read command must be supported by the Flash Memory)

- Waveform format: E Ink's waveform version 1 and version 2 (voltage controlled waveform)

#### 2.8 Clock Source

- Internal Programmable PLL

- Single clock input: CLKI

- Two terminal Crystal interface: OSCI/OSCO

#### 2.9 Miscellaneous

- Sleep and Standby Power Save Modes

- General Purpose Input/Output pins are available (GPIO[1:0])

- Interrupt pin associated with selectable GPIO inputs

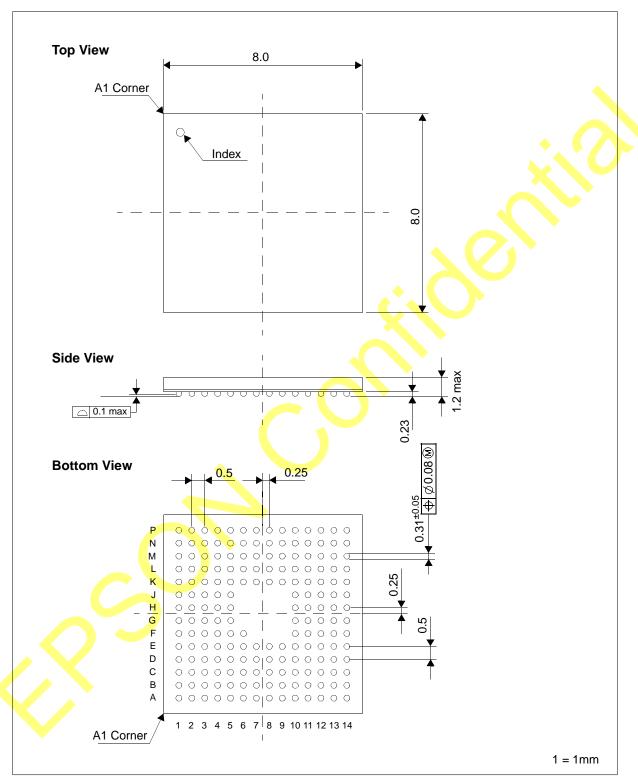

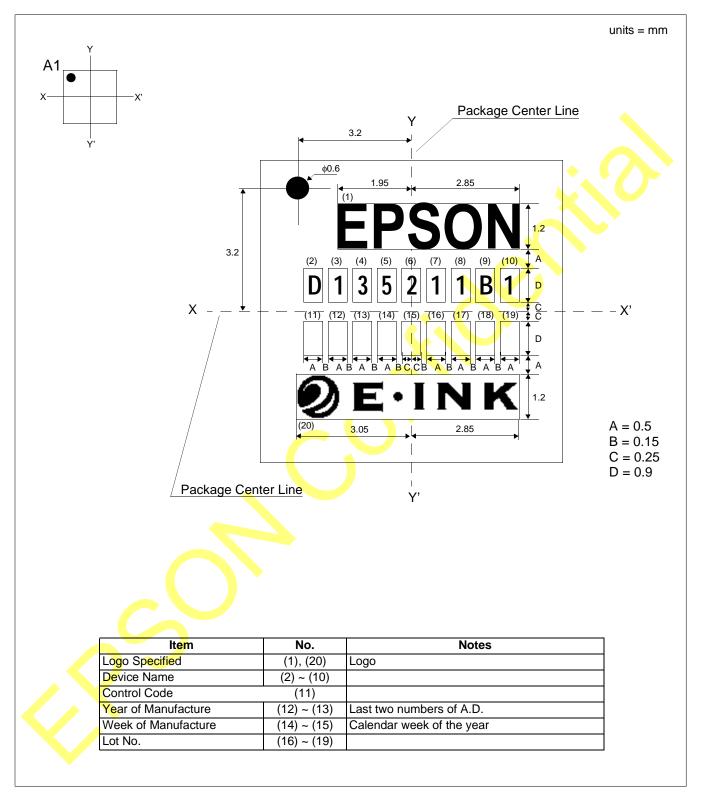

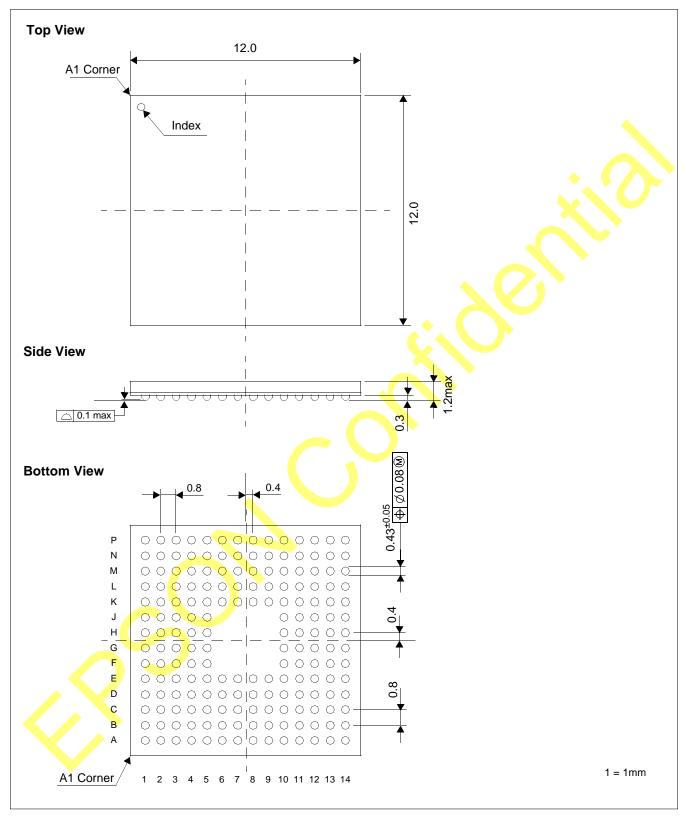

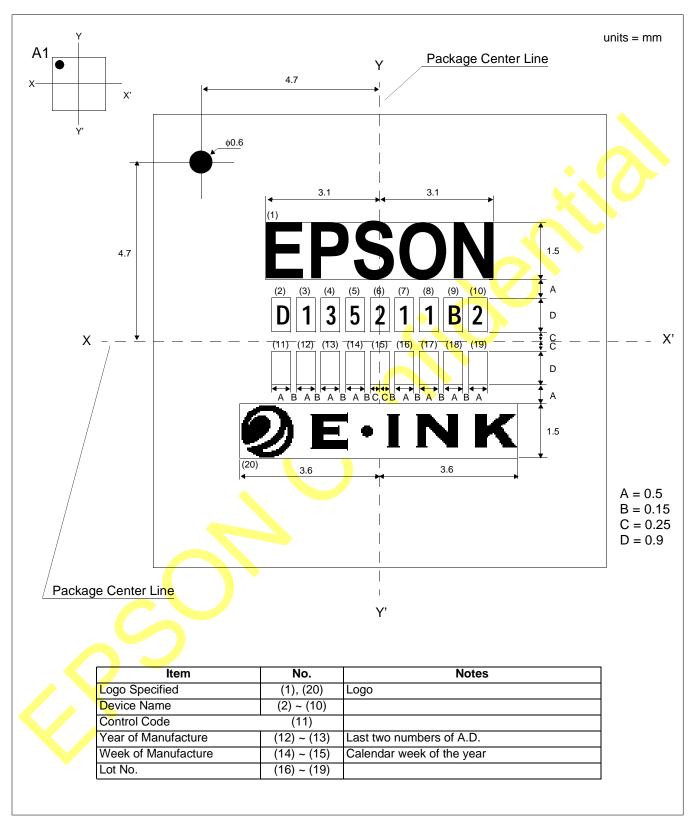

- Packages:

- PFBGA8UX 181-pin (8mm x 8mm x 1.2mm, 0.5mm ball pitch)

- PFBGA12UX 180-pin (12mm x 12mm x 1.2mm, 0.8mm ball pitch)

- Core Voltage: 1.8V

- IO Voltage: 1.8V ~ 3.3V (typical)

# **Chapter 3 Block Diagram**

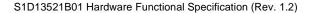

Figure 3-1: S1D13521 Block Diagram

## 3.1 Typical System Implementation

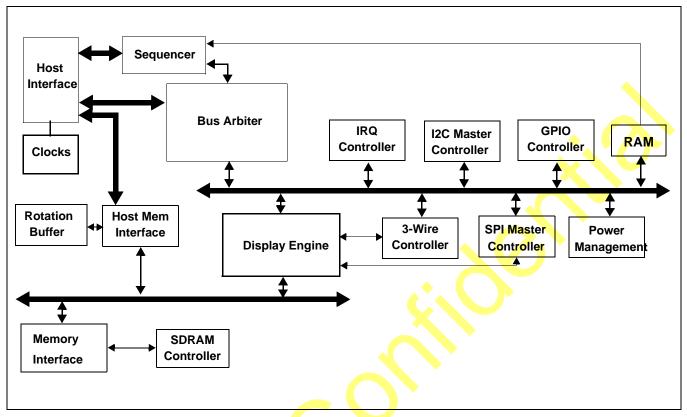

Figure 3-2: S1D13521 Typical System Implementation

#### Note

The Flash Memory must support the Fast Read command. For detailed Flash Memory requirements, see 17.3, "Serial Flash Memory" on page 136.

# **Chapter 4 Pins**

## 4.1 Pinout Diagram

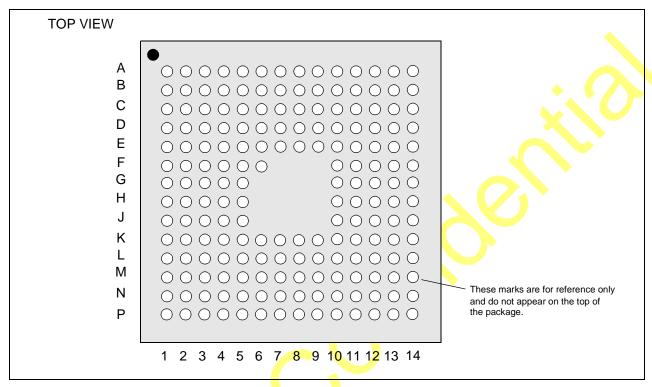

Figure 4-1: S1D13521 PFBGA8UX 181-pin Pin Mapping (Top View)

Table 4-1: S1D13521 PFBGA8UX 181-pin Pinout (Top View)

|   | 1       | 2       | 3      | 4        | 5       | 6        | 7        | 8        | 9        | 10       | 11       | 12       | 13       | 14       |   |

|---|---------|---------|--------|----------|---------|----------|----------|----------|----------|----------|----------|----------|----------|----------|---|

| Α | VSS     | TI2CD   | SPICLK | GDCLK    | GDRL    | SDDO14   | SDDO10   | PIOVDD   | SDDO2    | SDCE_L2  | SDCE_L5  | SDCE_L8  | SDSHR    | VSS      | Α |

| В | PWR3    | PPIOVDD | TI2CC  | GDSP     | GDOE    | SDD013   | SDDO9    | SDD05    | SDD01    | SDCE_L3  | SDCE_L6  | SDOEX    | SDOE     | SDCLK    | В |

| С | PWIOVDD | PWR1    | PWR2   | SPIDCS_L | SDDO15  | SDDO12   | SDD08    | SDDO4    | SDD00    | VSS      | SDCE_L7  | SDOED    | SDLE     | SDRIOVDD | С |

| D | PWRCOM  | BDR3    | PWR0   | VSS      | SPIDO   | SDD011   | SDD07    | SDD03    | SDCE_L0  | SDCE_L4  | SDRDAT26 | SDRDAT24 | SDRDAT21 | SDRDAT23 | D |

| Ε | OSCI    | OSCVDD  | BDR1   | BDR2     | SPIDI   | COREVDD  | SDD06    | VSS      | SDCE_L1  | PIOVDD   | SDRDAT28 | SDRDAT27 | SDRDAT19 | SDRDAT20 | Ε |

| F | osco    | oscvss  | VSS    | COREVDD  | BDR0    | VSS      |          |          |          | VSS      | SDRDAT25 | SDRDAT29 | SDRDAT22 | VSS      | F |

| G | VCP     | PLLVSS  | PLLVDD | HDB15    | HDB14   |          | _        |          |          | COREVDD  | SDRDAT30 | SDRDAT31 | SDRDAT18 | SDRDAT17 | G |

| Н | CLKI    | VSS     | HIRQ   | HDB13    | HIOVDD  |          |          |          |          | SDRIOVDD | SDRADR12 | SDRDQM3  | SDRDQM2  | SDRDAT16 | Н |

| J | VSS     | RESET_L | VSS    | HRD_L    | COREVDD |          |          |          |          | COREVDD  | VSS      | SDRADR3  | SDRADR1  | SDRADR2  | J |

| K | HWE_L   | CNF2    | HDB12  | HDB11    | CNF0    | HIOVDD   | VSS      | SDRIOVDD | COREVDD  | VSS      | SDRADR9  | SDRADR4  | SDRADR10 | SDRADR0  | K |

| L | HD/C    | HDB10   | HDB9   | HDB8     | HRDY    | HCS_L    | SDRDAT13 | SDRDAT14 | VSS      | SDRWE#   | SDRDQM1  | SDRADR5  | SDRBA1   | SDRADR11 | L |

| М | CNF1    | SCANEN  | GPI01  | HDB5     | HDB2    | SDRDAT15 | SDRDAT11 | SDRDAT12 | SDRDAT10 | SDRCAS#  | SDRCS#   | SDRADR6  | SDRADR7  | SDRRAS#  | М |

| Ν | TESTEN  | HDB7    | HDB6   | HDB4     | HDB1    | SDRDAT0  | SDRDAT4  | SDRDAT3  | SDRDAT9  | SDRDAT8  | SDRBA0   | SDRCKE   | SDRIOVDD | SDRADR8  | Ν |

| Р | VSS     | CNF3    | GPI00  | HDB3     | HDB0    | SDRDAT2  | SDRDAT1  | SDRDAT6  | SDRDAT5  | SDRDAT7  | SDRDQM0  | VSS      | SDRCLK   | VSS      | Р |

|   | 1       | 2       | 3      | 4        | 5       | 6        | 7        | 8        | 9        | 10       | 11       | 12       | 13       | 14       | , |

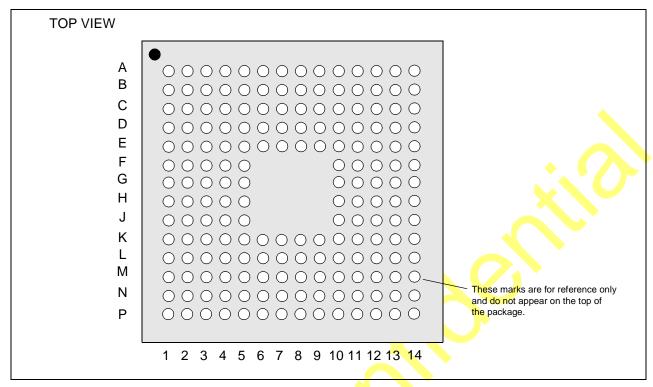

Figure 4-2: S1D13521 PFBGA12UX 180-pin Pin Mapping (Top View)

|   | 1       | 2       | 3      | 4                   | 5       | 6        | 7        | 8        | 9        | 10       | 11       | 12       | 13       | 14       |   |

|---|---------|---------|--------|---------------------|---------|----------|----------|----------|----------|----------|----------|----------|----------|----------|---|

| Α | VSS     | TI2CD   | SPICLK | GDCLK               | GDRL    | SDDO14   | SDDO10   | PIOVDD   | SDD02    | SDCE_L2  | SDCE_L5  | SDCE_L8  | SDSHR    | VSS      | Α |

| В | PWR3    | PPIOVDD | TI2CC  | GDSP                | GDOE    | SDDO13   | SDD09    | SDD05    | SDD01    | SDCE_L3  | SDCE_L6  | SDOEX    | SDOE     | SDCLK    | В |

| С | PWIOVDD | PWR1    | PWR2   | SPIDCS_L            | SDDO15  | SDDO12   | SDDO8    | SDD04    | SDD00    | VSS      | SDCE_L7  | SDOED    | SDLE     | SDRIOVDD | С |

| D | PWRCOM  | BDR3    | PWR0   | VSS                 | SPIDO   | SDD011   | SDD07    | SDD03    | SDCE_L0  | SDCE_L4  | SDRDAT26 | SDRDAT24 | SDRDAT21 | SDRDAT23 | D |

| Е | OSCI    | OSCVDD  | BDR1   | BDR2                | SPIDI   | COREVDD  | SDD06    | VSS      | SDCE_L1  | PIOVDD   | SDRDAT28 | SDRDAT27 | SDRDAT19 | SDRDAT20 | Е |

| F | osco    | oscvss  | VSS    | COREVDD             | BDR0    |          |          |          |          | VSS      | SDRDAT25 | SDRDAT29 | SDRDAT22 | VSS      | F |

| G | VCP     | PLLVSS  | PLLVDD | HDB15               | HDB14   |          |          |          |          | COREVDD  | SDRDAT30 | SDRDAT31 | SDRDAT18 | SDRDAT17 | G |

| Н | CLKI    | VSS     | HIRQ   | HDB13               | HIOVDD  |          |          |          |          | SDRIOVDD | SDRADR12 | SDRDQM3  | SDRDQM2  | SDRDAT16 | Н |

| J | VSS     | RESET_L | VSS    | HRD_L               | COREVDD |          |          |          |          | COREVDD  | VSS      | SDRADR3  | SDRADR1  | SDRADR2  | J |

| K | HWE_L   | CNF2    | HDB12  | HDB11               | CNF0    | HIOVDD   | VSS      | SDRIOVDD | COREVDD  | VSS      | SDRADR9  | SDRADR4  | SDRADR10 | SDRADR0  | K |

| L | HD/C    | HDB10   | HDB9   | HDB8                | HRDY    | HCS_L    | SDRDAT13 | SDRDAT14 | VSS      | SDRWE#   | SDRDQM1  | SDRADR5  | SDRBA1   | SDRADR11 | L |

| M | CNF1    | SCANEN  | GPI01  | HD <mark>B</mark> 5 | HDB2    | SDRDAT15 | SDRDAT11 | SDRDAT12 | SDRDAT10 | SDRCAS#  | SDRCS#   | SDRADR6  | SDRADR7  | SDRRAS#  | М |

|   |         |         |        |                     |         |          |          |          |          |          |          |          |          |          |   |

SDRDAT0 | SDRDAT4 | SDRDAT3 | SDRDAT9 | SDRDAT8

SDRDAT1 SDRDAT6 SDRDAT5 SDRDAT7

HDB4

HDB3

HDB1

HDB0

SDRDAT2

HDB6

GPI00

TESTEN

VSS

HDB7

CNF3

SDRBA0 SDRCKE SDRIOVDD SDRADR8 N

SDRCLK

13

VSS

14

VSS

12

SDRDQM0

## 4.2 Pin Descriptions

#### Key:

#### Pin Types

$egin{array}{lll} I & = & Input \\ O & = & Output \end{array}$

IO = Bi-Directional (Input/Output)

P = Power pin

#### **RESET# States**

H = High level output

L = Low level output

Z = High Impedance (Hi-Z)

1 = Pull-up resistor on input

0 = Pull-down resistor on input

# = Active low level

Table 4-3: Cell Descriptions

| Item  | Description                                                                                |

|-------|--------------------------------------------------------------------------------------------|

| IC    | High voltage LVCMOS input buffer                                                           |

| ICS   | High voltage LVCMOS Schmitt input buffer                                                   |

| ICD2  | High voltage LVCMOS input buffer with pull-down (100kΩ@3.3V)                               |

| 0     | High voltage low noise output buffer (4mA@3.3V)                                            |

| ОН    | High voltage high speed output buffer (4mA@3.3V)                                           |

| BC    | High voltage LVCMOS low noise bi-directional buffer (4mA@3.3V)                             |

| BCS   | High voltage LVCMOS schmitt low noise bi-directional buffer (4mA@3.3V)                     |

| BCD2  | High voltage LVCMOS low noise bi-directional buffer (4mA@3.3V) with pull-down (100kΩ@3.3V) |

| ВСН   | High voltage LVCMOS high speed bi-directional buffer (4mA@3.3V)                            |

| ILTR  | Low voltage transparent input buffer                                                       |

| OLTR  | Low volta <mark>ge</mark> transp <mark>are</mark> nt output buffer                         |

| ILTSD | Low volta <mark>ge</mark> test mod <mark>e</mark> control input buffer with pull-down      |

#### Note

Unless otherwise specified, unused pins must be connected to VSS through a  $100\Omega$  resistor.

#### 4.2.1 Shared Host Interface

Table 4-4: Shared Host Interface Pin Descriptions

| Pin Name | Туре | Pin# | Cell | Power  | RESET_L<br>State | Description                                                                                                                                                                                                                                        |

|----------|------|------|------|--------|------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| RESET_L  | ı    | J2   | ICS  | HIOVDD | _                | This active low input sets all internal registers to their default states and forces all signals to their inactive states. When unused, this pin should be connected to HIOVDD.  For RESET_L timing details, see 6.3, "RESET_L Timing" on page 33. |

| HIRQ     | 0    | H3   | 0    | HIOVDD | L                | This output pin is the Host IRQ.                                                                                                                                                                                                                   |

#### 4.2.2 Host Interface

Table 4-5: Host Interface Pin Descriptions

| Pin Name  | Туре | Pin#                                                                          | Cell | Power  | RESET_L<br>State | Description                                                        |

|-----------|------|-------------------------------------------------------------------------------|------|--------|------------------|--------------------------------------------------------------------|

| HDB[15:0] | Ю    | G4, G5, H4,<br>K3, K4, L2,<br>L3, L4, N2,<br>N3, M4, N4,<br>P4, M5, N5,<br>P5 | ВС   | HIOVDD | Z                | These pins are the shared command/parameter lines 15-0.            |

| HWE_L     | I    | K1                                                                            | ICS  | HIOVDD | , (-             | This input pin is the Write Enable signal.                         |

| HRD_L     | I    | J4                                                                            | ICS  | HIOVDD | _                | This input pin is the Read Enable signal.                          |

| HCS_L     | I    | L6                                                                            | IC   | HIOVDD | -                | This input pin is the Chip Select signal.                          |

| HD/C      | I    | L1                                                                            | IC   | HIOVDD | _                | This input pin selects between Command (Low) and Parameter (High). |

| HRDY      | Ю    | L5                                                                            | ВС   | HIOVDD | H<br>(see Note)  | This active high pin is the Host interface Ready (or WAIT) signal. |

#### Note

The RESET\_L state of the HRDY pin is Low while the command sequencer loads the instruction code from the Serial Flash Memory.

## 4.2.3 SDRAM Interface

Table 4-6: SDRAM Interface Pin Descriptions

| Pin Name     | Туре | Pin#                                                                                                                                                                                    | Cell | Power    | RESET_L    | Description                                        |

|--------------|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|----------|------------|----------------------------------------------------|

| SDRADR[12:0] | 0    | H11, L14,<br>K13, K11,<br>N14, M13,<br>M12, L12<br>K12, J12,<br>J14, J13, K14                                                                                                           | ОН   | SDRIOVDD | State<br>L | These output pins are the SDRAM Address pins.      |

| SDRBA[1:0]   | 0    | L13, N11                                                                                                                                                                                | ОН   | SDRIOVDD | L          | These output pins are the SDRAM Bank Address pins. |

| SDRCAS#      | 0    | M10                                                                                                                                                                                     | ОН   | SDRIOVDD | Н          | This output pin is the SDRAM CAS# pin.             |

| SDRRAS#      | 0    | M14                                                                                                                                                                                     | ОН   | SDRIOVDD | Н          | This output pin is the SDRAM RAS# pin.             |

| SDRCS#       | 0    | M11                                                                                                                                                                                     | ОН   | SDRIOVDD | L          | This output pin is the SDRAM CS# pin.              |

| SDRWE#       | 0    | L10                                                                                                                                                                                     | ОН   | SDRIOVDD | Н          | This output pin is the SDRAM WE# pin.              |

| SDRDQM[3:0]  | 0    | H12, H13,<br>L11, P11                                                                                                                                                                   | ОН   | SDRIOVDD | Н          | These output pins are the SDRAM DQM pins.          |

| SDRCKE       | 0    | N12                                                                                                                                                                                     | ОН   | SDRIOVDD | Н          | This output pin is the SDRAM CKE pin.              |

| SDRCLK       | 0    | P13                                                                                                                                                                                     | ОН   | SDRIOVDD | Н          | This output pin is the SDRAM CLK pin.              |

| SDRDAT[31:0] | Ю    | G12, G11,<br>F12, E11,<br>E12, D11,<br>F11, D12,<br>D14, F13,<br>D13, E14,<br>E13, G13,<br>G14, H14,<br>M6, L8, L7,<br>M8, M7, M9,<br>N9, N10, P10,<br>P8, P9, N7,<br>N8, P6, P7,<br>N6 | всн  | SDRIOVDD |            | These input/output pins are the SDRAM DATA pins.   |

#### 4.2.4 SPI Master Interface for Serial Flash

Table 4-7: SPI Master Interface Pin Descriptions

| Pin Name | Туре | Pin # | Cell | Power   | RESET_L<br>State | Description                                                     |  |

|----------|------|-------|------|---------|------------------|-----------------------------------------------------------------|--|

| SPIDCS_L | 0    | C4    | 0    | PPIOVDD | Н                | This output pin is the Slave Chip Select for the SPI interface. |  |

| SPICLK   | 0    | А3    | 0    | PPIOVDD | L                | This output pin is the Slave Clock for the SPI interface.       |  |

| SPIDO    | 0    | D5    | 0    | PPIOVDD | L                | This pin is the data output for the SPI interface.              |  |

| SPIDI    | I    | E5    | IC   | PPIOVDD | _                | This pin is the data input for the SPI interface.               |  |

#### 4.2.5 I2C Master Interface for Thermal Sensor

Table 4-8: I2C Master Interface Pin Descriptions

| Pin Name | Туре | Pin# | Cell | Power   | RESET_L<br>State | Description                                                                                                      |  |

|----------|------|------|------|---------|------------------|------------------------------------------------------------------------------------------------------------------|--|

| TI2CC    | Ю    | В3   | BCS  | PPIOVDD |                  | This input/output pin is the I2C Master Serial Clock.  If this pin is not used, it must be connected to PPIOVDD. |  |

| TI2CD    | Ю    | A2   | BCS  | PPIOVDD |                  | This input/output pin is the I2C Master Data.  If this pin is not used, it must be connected to PPIOVDD.         |  |

#### 4.2.6 Gate Driver Interface

Table 4-9: Gate Driver Interface Pin Descriptions

| Pin Name | Туре                                                           | Pin# | Cell                                                      | Power  | RESET_L<br>State | Description                                       |  |

|----------|----------------------------------------------------------------|------|-----------------------------------------------------------|--------|------------------|---------------------------------------------------|--|

| GDCLK    | 0                                                              | A4   | 0                                                         | PIOVDD | L                | This output pin is the clock for the Gate Driver. |  |

| GDSP     | 0                                                              | B4   | 0                                                         | PIOVDD | Н                | This output pin is the Gate Driver Start Pulse.   |  |

| GDOE     | O B5 O PIOVDD L This output pin is the output enable for the G |      | This output pin is the output enable for the Gate Driver. |        |                  |                                                   |  |

| GDRL     | 0                                                              | A5   | 0                                                         | PIOVDD | L                | This output pin is the Gate Driver Right or Left. |  |

## 4.2.7 Source Driver Interface

Table 4-10: Source Driver Interface Pin Descriptions

| Pin Name    | Туре | Pin#                                                                          | Cell | Power  | RESET_L<br>State | Description                                                                                                                                                                                                                                                   |  |

|-------------|------|-------------------------------------------------------------------------------|------|--------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| SDCLK       | 0    | B14                                                                           | 0    | PIOVDD | L                | This output pin is the clock for the Source Driver.                                                                                                                                                                                                           |  |

| SDLE        | 0    | C13                                                                           | 0    | PIOVDD | L                | This output pin is the latch enable for the Source Driver.                                                                                                                                                                                                    |  |

| SDDO[15:0]  | 0    | C5, A6, B6,<br>C6, D6, A7,<br>B7, C7, D7,<br>E7, B8, C8,<br>D8, A9, B9,<br>C9 | 0    | PIOVDD | L                | These are the data output pins for the Source Driver.                                                                                                                                                                                                         |  |

| SDOED       | 0    | C12                                                                           | 0    | PIOVDD | L                | This output is the SDOED pin used for Double Data Rate Source Driver output.                                                                                                                                                                                  |  |

| SDOEX       | 0    | B12                                                                           | 0    | PIOVDD | L                | This output is the SDOEX pin used for Double Data<br>Rate Source Driver output.                                                                                                                                                                               |  |

| SDCE_L[8:0] | 0    | A12, C11,<br>B11, A11,<br>D10, B10,<br>A10, E9, D9                            | 0    | PIOVDD | Н                | These output pins are the Source Driver Chip Enables 8-0.  For details on the configurability of these pins, refer to A.3.14, "Display Engine: Driver Configurations" on page 208 (see REG[030Ch]) and 6.5.2, "Interpreted Source Driver Timings" on page 39. |  |

| SDSHR       | 0    | A13                                                                           | 0    | PIOVDD | L                | This output pin is the Source Driver Shift Right Enable.                                                                                                                                                                                                      |  |

| SDOE        | 0    | B13                                                                           | 0    | PIOVDD |                  | This output pin is the output enable for the Source Driver.                                                                                                                                                                                                   |  |

#### 4.2.8 Power Switches Control Interface

The power control interface signals have dual function pins.

- 1. Power sequence output (default power-on function)

- 2. 3-wire Active Matrix Power Management ICs

Table 4-11: Power Switches Control Interface Pin Descriptions

| Pin Name          | Туре | Pin# | Cell | Power   | RESET_L<br>State | Description                                                                                                                                                                                                             |  |

|-------------------|------|------|------|---------|------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| PWR0/<br>DAPWRALL | Ю    | D3   | вс   | PWIOVDD | L                | These input/output pins have multiple functions.  Power Control Signal 0 (PWR0). For timing details, see 6.6.1, "Power Pin Transition Sequence for PWR[3:0]" on page 48.  3-wire Power All Pin output (DAPWRALL)        |  |

| PWR1/DACLK        | Ю    | C2   | вс   | PWIOVDD | L                | These input/output pins have multiple functions.  • Power Control Signal 1 (PWR1). For timing detai see 6.6.1, "Power Pin Transition Sequence for PWR[3:0]" on page 48.  • 3-wire Serial Clock (DACLK)                  |  |

| PWR2/DADIO        | Ю    | СЗ   | ВС   | PWIOVDD | L                | These input/output pins have multiple functions.  • Power Control Signal 2 (PWR2). For timing details see 6.6.1, "Power Pin Transition Sequence for PWR[3:0]" on page 48.  • 3-wire data tri-state input/output (DADIO) |  |

| PWR3/<br>DACEB    | Ю    | B1   | ВС   | PWIOVDD |                  | These input/output pins have multiple functions.  • Power Control Signal 3 (PWR3). For timing details, see 6.6.1, "Power Pin Transition Sequence for PWR[3:0]" on page 48.  • 3-wire active low enable (DACEB)          |  |

| PWRCOM            | 0    | D1   | 0    | PWIOVDD | L                | Display Common Power Signals. For timing details, see 6.6.2, "Power Pin Transition Sequence for PWRCOM" on page 49.                                                                                                     |  |

## 4.2.9 Display Border Power Interface

Table 4-12: Display Border Power Interface Pin Descriptions

| Pin Name | Туре | Pin #             | Cell | Power   | RESET_L<br>State | Description                                             |

|----------|------|-------------------|------|---------|------------------|---------------------------------------------------------|

| BDR[3:0] | 0    | D2, E4, E3,<br>F5 | 0    | PWIOVDD | L                | These output pins are the Display Border Power Signals. |

## 4.2.10 Miscellaneous

Table 4-13: Miscellaneous Pin Descriptions

| Pin Name  | Туре | Pin #             | Cell  | Power    | RESET_L<br>State | Description                                                                                                                                                                                                         |

|-----------|------|-------------------|-------|----------|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CLKI      | I    | H1                | ICS   | HIOVDD   | _                | This pin is the clock input. For details on the clock structure, see Chapter 7, "Clocks" on page 50.  If unused, this pin must be connected to VSS.                                                                 |

| OSCI      | I    | E1                | ILTR  | OSCVDD — |                  | This pin is the input for the 2-terminal crystal interface. When the internal oscillator is not used, this pin must be connected to OSCVDD. For details on the clock structure, see Chapter 7, "Clocks" on page 50. |

| osco      | 0    | F1                | OLTR  | OSCVDD   | Н                | This pin is the output for the 2-terminal crystal interface. When the internal oscillator is not used, this pin must be left unconnected. For details on the clock structure, see Chapter 7, "Clocks" on page 50.   |

| CNF[3:0]  | I    | P2, K2, M1,<br>K5 | IC    | HIOVDD   | _                | These input pins are used for configuring the S1D13521 and must be connected to either HIOVDD or VSS. For a summary of configuration options, see 4.3, "Configuration Pins" on page 24.                             |

| GPIO[1:0] | Ю    | M3, P3            | BCD2  | HIOVDD   | Z                | These are the General Purpose Input/Output pins.                                                                                                                                                                    |

| TESTEN    | I    | N1                | ILTSD | HIOVDD   | _                | This input pin is the Test Enable pin and is used for production test only. This pin should be left unconnected for normal operation.                                                                               |

| SCANEN    | I    | M2                | ICD2  | HIOVDD   | •                | This input pin is the Scan Enable pin and is used for production test only. This pin should be left unconnected for normal operation.                                                                               |

| VCP       | 0    | G1                | OLTR  | PLLVDD   | •                | This output pin is for production test only and must be left unconnected for normal operation.                                                                                                                      |

#### 4.2.11 Power and Ground

Table 4-14: Power And Ground Pin Descriptions

| Pin Name          | Туре | Pin#                                                                                                       | Cell | Power     | RESET_L<br>State | Description                                                     |  |

|-------------------|------|------------------------------------------------------------------------------------------------------------|------|-----------|------------------|-----------------------------------------------------------------|--|

| HIOVDD            | Р    | H5, K6                                                                                                     | Р    | 1.65-3.6V | _                | IO power supply for the Host interface                          |  |

| SDRIOVDD          | Р    | C14, H10,<br>K8, N13                                                                                       | Р    | 1.8/3.3V  | _                | IO power supply for the SDRAM interface                         |  |

| PPIOVDD           | Р    | B2                                                                                                         | Р    | 1.65-3.6V | _                | IO power supply for the SPI and I2C interface                   |  |

| PWIOVDD           | Р    | C1                                                                                                         | Р    | 1.65-3.6V | _                | IO power supply for Power Switch & Display Border control       |  |

| PIOVDD            | Р    | A8, E10                                                                                                    | Р    | 1.65-3.6V | _                | IO power supply for Source and Gate Driver                      |  |

| COREVDD           | Р    | E6, F4,<br>G10, J5,<br>J10, K9                                                                             | Р    | 1.8V      | _                | Core power supply                                               |  |

| VSS<br>(see Note) | Р    | A1, A14,<br>C10, D4,<br>E8, F3, F6,<br>F10, F14,<br>H2, J1, J3,<br>J11, K7,<br>K10, L9,<br>P1, P12,<br>P14 | Р    | 0         | _                | GND for HIOVDD, SDRIOVDD, PPIOVDD, PWIOVDD, PIOVDD, and COREVDD |  |

| PLLVDD            | Р    | G3                                                                                                         | Р    | 1.8V      | _                | PLL power supply                                                |  |

| PLLVSS            | Р    | G2                                                                                                         | Р    | 0         | -                | GND for PLLVDD                                                  |  |

| OSCVDD            | Р    | E2                                                                                                         | Р    | 1.8V      | 7                | OSC power supply                                                |  |

| OSCVSS            | Р    | F2                                                                                                         | Р    | 0         | GND for OSCVDD   |                                                                 |  |

#### Note

For the PFBGA12UX 180-pin package, there is no F6 pin.

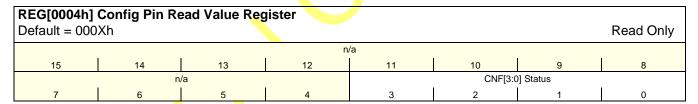

## 4.3 Configuration Pins

The S1D13521 has four configuration pins, CNF[3:0], which must be connected to HIOVDD or VSS according to the following table.

*Table 4-15: Configuration Pin Summary*

| CNF[3:0] | 1 (connected to HIOVDD)                                 | 0 (connected to VSS)                            |  |  |  |  |

|----------|---------------------------------------------------------|-------------------------------------------------|--|--|--|--|

| CNF3     | HRDY only driven when HCS_L is asserted                 | HRDY is always driven                           |  |  |  |  |

| CNF2     | OSCI/OSCO is the source for the Input Clock. (see Note) | CLKI is the source for the Input Clock.         |  |  |  |  |

| CNF1     | Reserved. This pin must be connected to HIO\            | Reserved. This pin must be connected to HIOVDD. |  |  |  |  |

| CNF0     | Reserved. This pin must be connected to VSS             |                                                 |  |  |  |  |

#### Note

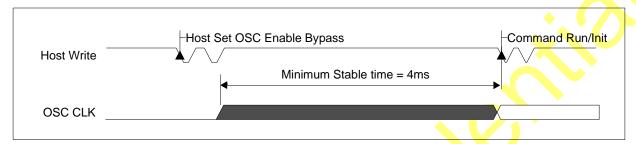

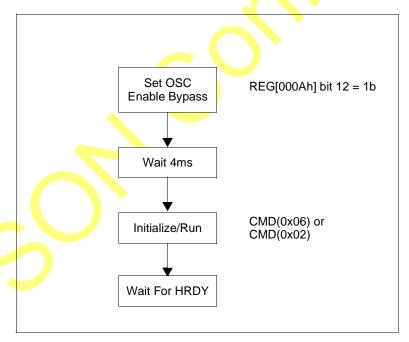

When using the internal oscillator (CNF2=1), there are timing requirements that must be observed or the Command Interface hardware will not be able to perform a normal boot-up initialization sequence which will result in a system failure for the S1D13521. For details on these timing requirements, refer to Chapter 18, "OSC Clock Timing Requirements" on page 145.

## 4.4 Pin Mapping

#### 4.4.1 Source Driver Interface

The Source Driver output width is dependent on the Pixel Output Count Select bit (see REG[030Ch] bit 11).

Table 4-16: Source Driver Interface Bitwidth Select

| Pin Name    | •                   | ount Select = 0<br>er SDCLK) | Pixel Output Count Select = 1 (8 pixels per SDCLK) |                     |  |

|-------------|---------------------|------------------------------|----------------------------------------------------|---------------------|--|

| Fill Name   | 2-bit Voltage Level | 4-bit Voltage Level          | 2-bit Voltage Level                                | 4-bit Voltage Level |  |

|             | Control             | Control                      | Control                                            | Control             |  |

| SDCLK       | SDCLK               | SDCLK                        | SDCLK                                              |                     |  |

| SDLE        | SDLE                | SDLE                         | SDLE                                               |                     |  |

| SDDO[1:0]   | Pixel 0[1:0]        | Pixel 0[1:0]                 | Pixel 0[1:0]                                       |                     |  |

| SDDO[3:2]   | Pixel 1[1:0]        | Pixel 0[2:3]                 | Pixel 1[1:0]                                       |                     |  |

| SDDO[5:4]   | Pixel 2[1:0]        | Pixel 1[1:0]                 | Pixel 2[1:0]                                       |                     |  |

| SDDO[7:6]   | Pixel 3[1:0]        | Pixel 1[2:3]                 | Pixel 3[1:0]                                       |                     |  |

| SDDO[9:8]   | driven 0            | Pixel 2[1:0]                 | Pixel 4[1:0]                                       |                     |  |

| SDDO[11:10] | driven 0            | Pixel 2[2:3]                 | Pixel 5[1:0]                                       |                     |  |

| SDDO[13:12] | driven 0            | Pixel 3[1:0]                 | Pixel 6[1:0]                                       | No Supported Mode   |  |

| SDDO[15:14] | driven 0            | Pixel 3[2 <mark>:3</mark> ]  | Pixel 7[1:0]                                       |                     |  |

| SDOED       | driven 0            | driven 0                     | driven 0 for non-DDR<br>SDOED for DDR              |                     |  |

| SDOEX       | driven 0            | driven 0                     | driven 0 for non-DDR<br>SDOEX for DDR              |                     |  |

| SDCE_L[8:0] | SDCE_L[8:0]         | SDCE_L[8:0]                  | SDCE_L[8:0]                                        |                     |  |

| SDSHR       | SDSHR               | SDSHR                        | SDSHR                                              |                     |  |

| SDOE        | SDOE                | SDOE                         | SDOE                                               |                     |  |

#### 4.4.2 Border Pin Interface

Table 4-17: Border Pin Interface Bitwidth Select

| Pin Name | 2-bit Voltage Level Control | 4-bit Voltage Level Control |

|----------|-----------------------------|-----------------------------|

| BDR[1:0] | Border Value[1:0]           | Border Value[1:0]           |

| BDR[3:2] | Driven 0                    | Border Value[2:3]           |

# Chapter 5 D.C. Characteristics

## 5.1 Absolute Maximum Ratings

Table 5-1: Absolute Maximum Ratings

| Symbol                | Parameter                              | Rating                                            | Units |

|-----------------------|----------------------------------------|---------------------------------------------------|-------|

| Core V <sub>DD</sub>  | Core Supply Voltage                    | V <sub>SS</sub> - 0.3 ~ 2.5                       | V     |

| PLL V <sub>DD</sub>   | PLL Supply Voltage                     | V <sub>SS</sub> - 0.3 ~ 2.5                       | V     |

| OSC V <sub>DD</sub>   | OSC Supply Voltage                     | V <sub>SS</sub> - 0.3 ~ 2.5                       | V     |

| HIO V <sub>DD</sub>   | Host IO Supply Voltage                 | V <sub>SS</sub> - 0.3 ~ 4.0                       | V     |

| PIO V <sub>DD</sub>   | Gate/Source IO Supply Voltage          | V <sub>SS</sub> - 0.3 ~ 4.0                       | V     |

| SDRIO V <sub>DD</sub> | SDRAM IO Supply Voltage                | V <sub>SS</sub> - 0.3 ~ 4.0                       | V     |

| PPIO V <sub>DD</sub>  | SPI and I2C IO Supply Voltage          | V <sub>SS</sub> - 0.3 ~ 4.0                       | V     |

| PWIO V <sub>DD</sub>  | Power Switch Control IO Supply Voltage | V <sub>SS</sub> - 0.3 ~ 4.0                       | V     |

| V <sub>IN</sub>       | Input Signal Voltage                   | V <sub>SS</sub> - 0.3 ~ *IO V <sub>DD</sub> + 0.5 | V     |

| V <sub>OUT</sub>      | Output Signal Voltage                  | V <sub>SS</sub> - 0.3 ~ *IO V <sub>DD</sub> + 0.5 | V     |

| I <sub>OUT</sub>      | Output Signal Current                  | ±10                                               | mA    |

| T <sub>STG</sub>      | Storage Temperature                    | -6 <mark>5 ~ 1</mark> 50                          | °C    |

#### Note

$V_{SS} = 0 V$

Core  $V_{DD}$ , PLL  $V_{DD}$ , OSC  $V_{DD} \le *IOV_{DD}$

# 5.2 Recommended Operating Conditions

Table 5-2: Recommended Operating Conditions

| Symbol                | Parameter                              | Condition             | Min             | Тур  | Max                 | Units |

|-----------------------|----------------------------------------|-----------------------|-----------------|------|---------------------|-------|

| Core V <sub>DD</sub>  | Core Supply Voltage                    | V <sub>SS</sub> = 0 V | 1.65            | 1.80 | 1.95                | V     |

| PLL V <sub>DD</sub>   | PLL Supply Voltage                     | V <sub>SS</sub> = 0 V | 1.65            | 1.80 | 1.95                | V     |

| OSC V <sub>DD</sub>   | OSC Supply Voltage                     | V <sub>SS</sub> = 0 V | 1.65            | 1.80 | 1.95                | V     |

| HIO V <sub>DD</sub>   | Host IO Supply Voltage                 | V <sub>SS</sub> = 0 V | 1.65            | _    | 3.60                | V     |

| PIO V <sub>DD</sub>   | Gate/Source IO Supply Voltage          | V <sub>SS</sub> = 0 V | 1.65            | _    | 3.60                | V     |

| SDRIO V <sub>DD</sub> | SDRAM IO Supply Voltage                | V <sub>SS</sub> = 0 V | 1.65            | 1.80 | 1.95                | V     |

| SDKIO VDD             | SDKAW 10 Supply Voltage                | V <sub>SS</sub> = 0 V | 2.70            | 3.30 | 3.60                | V     |

| PPIO V <sub>DD</sub>  | SPI and I2C IO Supply Voltage          | V <sub>SS</sub> = 0 V | 1.65            | _    | 3.60                | V     |

| PWIO V <sub>DD</sub>  | Power Switch Control IO Supply Voltage | V <sub>SS</sub> = 0 V | 1.65            | _    | 3.60                | V     |

| V <sub>IN</sub>       | Input Voltage                          | _                     | V <sub>SS</sub> | _    | *IO V <sub>DD</sub> | V     |

| T <sub>OPR</sub>      | Operating Temperature                  | _                     | -40             | 25   | 85                  | °C    |

## **5.3 Electrical Characteristics**

Table 5-3: Electrical Characteristics for IO  $V_{DD} = 1.8V \pm 0.15V$

| Symbol           | Parameter                      | Condition                                                                  | Min  | Тур | Max                        | Units |

|------------------|--------------------------------|----------------------------------------------------------------------------|------|-----|----------------------------|-------|

| I <sub>DDS</sub> | Quiescent Current              | Quiescent Conditions                                                       | _    | 1.4 | _                          | μΑ    |

| I <sub>IZ</sub>  | Input Leakage Current          | _                                                                          | -5   |     | 5                          | μΑ    |

| I <sub>OZ</sub>  | Output Leakage Current         | _                                                                          | -5   | _   | 5                          | μΑ    |

| I <sub>OH</sub>  | High Level Output Current      | $ OV_{DD} = min$ $ V_{OH} =  OV_{DD} - 0.4 V $                             | -2   | _   | _                          | mA    |

| I <sub>OL</sub>  | Low Level Output Current       | $\begin{aligned} IOV_{DD} &= min \\ V_{OL} &= 0.4 \text{ V} \end{aligned}$ | 2    | _   | <b>+</b> , <del>-</del> // | mA    |

| V <sub>IH</sub>  | High Level Input Voltage       | LVCMOS Level<br>IO V <sub>DD</sub> = max                                   | 1.27 | _   | IO V <sub>DD</sub> + 0.3   | V     |

| V <sub>IL</sub>  | Low Level Input Voltage        | LVCMOS Level<br>IO V <sub>DD</sub> = min                                   | -0.3 | 1   | 0.57                       | V     |

| $V_{T+}$         | Positive Trigger Voltage       | LVCMOS Schmitt                                                             | 0.58 |     | 1.46                       | V     |

| V <sub>T-</sub>  | Negative Trigger Voltage       | LVCMOS Schmitt                                                             | 0.42 |     | 1.26                       | V     |

| $V_{H}$          | Hysteresis Voltage             | LVCMOS Schmitt                                                             | 0.17 |     | _                          | V     |

| R <sub>PD</sub>  | Pull-Down Resistance           | $V_{IN} = IO V_{DD}$                                                       | 96   | 240 | 600                        | kΩ    |

| C <sub>I</sub>   | Input Pin Capacitance          | f = 1MHz, IO V <sub>DD</sub> = 0V                                          |      | _   | 6                          | pF    |

| Co               | Output Pin Capacitance         | $f = 1MHz$ , IO $V_{DD} = 0V$                                              | _    | _   | 6                          | pF    |

| C <sub>IO</sub>  | Bi-Directional Pin Capacitance | $f = 1MHz$ , IO $V_{DD} = 0V$                                              | _    | _   | 6                          | pF    |

Table 5-4: Electrical Characteristics for IO  $V_{DD} = 2.5V \pm 0.2V$

| Symbol           | Parameter                      | Condition Condition                            | Min  | Тур | Max                      | Units |

|------------------|--------------------------------|------------------------------------------------|------|-----|--------------------------|-------|

| I <sub>DDS</sub> | Quiescent Current              | Quiescent Conditions                           | _    | 1.4 | _                        | μΑ    |

| $I_{IZ}$         | Input Leakage Current          | _                                              | -5   | _   | 5                        | μΑ    |

| I <sub>OZ</sub>  | Output Leakage Current         | -                                              | -5   | _   | 5                        | μΑ    |

| I <sub>OH</sub>  | High Level Output Current      | $IOV_{DD} = min$<br>$V_{OH} = IOV_{DD} - 0.4V$ | -3   | _   | _                        | mA    |

| I <sub>OL</sub>  | Low Level Output Current       | $IOV_{DD} = min$<br>$V_{OL} = 0.4 V$           | 3    | _   | _                        | mA    |

| V <sub>IH</sub>  | High Level Input Voltage       | LVCMOS Level<br>IO V <sub>DD</sub> = max       | 1.7  | _   | IO V <sub>DD</sub> + 0.3 | V     |

| V <sub>IL</sub>  | Low Level Input Voltage        | LVCMOS Level<br>IO V <sub>DD</sub> = min       | -0.3 | _   | 0.7                      | V     |

| $V_{T+}$         | Positive Trigger Voltage       | LVCMOS Schmitt                                 | 0.92 | _   | 1.89                     | V     |

| $V_{T-}$         | Negative Trigger Voltage       | LVCMOS Schmitt                                 | 0.58 | _   | 1.48                     | V     |

| V <sub>H</sub>   | Hysteresis Voltage             | LVCMOS Schmitt                                 | 0.23 | _   | _                        | V     |

| R <sub>PD</sub>  | Pull-Down Resistance           | $V_{IN} = IO V_{DD}$                           | 70   | 140 | 350                      | kΩ    |

| CI               | Input Pin Capacitance          | $f = 1MHz$ , $IO V_{DD} = 0V$                  | _    | _   | 6                        | pF    |

| Co               | Output Pin Capacitance         | $f = 1MHz$ , $IO V_{DD} = 0V$                  | _    | _   | 6                        | pF    |

| C <sub>IO</sub>  | Bi-Directional Pin Capacitance | $f = 1MHz$ , $IO V_{DD} = 0V$                  | _    | _   | 6                        | pF    |

Table 5-5: Electrical Characteristics for IO  $V_{DD}=3.3V\pm0.3V$

| Symbol           | Parameter                      | Condition                                      | Min  | Тур      | Max                      | Units |

|------------------|--------------------------------|------------------------------------------------|------|----------|--------------------------|-------|

| I <sub>DDS</sub> | Quiescent Current              | Quiescent Conditions                           | _    | 1.4      | _                        | μΑ    |

| I <sub>IZ</sub>  | Input Leakage Current          | _                                              | -5   | _        | 5                        | μΑ    |

| I <sub>OZ</sub>  | Output Leakage Current         | _                                              | -5   | _        | 5                        | μΑ    |

| I <sub>OH</sub>  | High Level Output Current      | $IOV_{DD} = min$<br>$V_{OH} = IOV_{DD} - 0.4V$ | -4   | _        | -                        | mA    |

| I <sub>OL</sub>  | Low Level Output Current       | $IOV_{DD} = min$<br>$V_{OL} = 0.4 V$           | 4    | _        | -                        | mA    |

| V <sub>IH</sub>  | High Level Input Voltage       | LVCMOS Level<br>IO V <sub>DD</sub> = max       | 2.2  | _        | IO V <sub>DD</sub> + 0.3 | V     |

| V <sub>IL</sub>  | Low Level Input Voltage        | LVCMOS Level<br>IO V <sub>DD</sub> = min       | -0.3 | _        | 0.8                      | V     |

| $V_{T+}$         | Positive Trigger Voltage       | LVCMOS Schmitt                                 | 1.2  | 7        | 2.52                     | V     |

| V <sub>T-</sub>  | Negative Trigger Voltage       | LVCMOS Schmitt                                 | 0.75 | _        | 1.98                     | V     |

| $V_{H}$          | Hysteresis Voltage             | LVCMOS Schmitt                                 | 0.3  | 0-1      | <u> </u>                 | V     |

| R <sub>PD</sub>  | Pull-Down Resistance           | $V_{IN} = IO V_{DD}$                           | 50   | 100      | 240                      | kΩ    |

| C <sub>I</sub>   | Input Pin Capacitance          | $f = 1MHz$ , $IO V_{DD} = 0V$                  |      |          | 6                        | pF    |

| Co               | Output Pin Capacitance         | f = 1MHz, IO V <sub>DD</sub> = 0V              |      | <u> </u> | 6                        | pF    |

| C <sub>IO</sub>  | Bi-Directional Pin Capacitance | $f = 1MHz$ , $IO V_{DD} = 0V$                  |      | _        | 6                        | pF    |

Table 5-6: Electrical Characteristics for CORE  $V_{DD}$

| Symbol           | Parameter              | Condition            | Min | Тур | Max | Units |

|------------------|------------------------|----------------------|-----|-----|-----|-------|

| I <sub>DDS</sub> | Quiescent Current      | Quiescent Conditions | _   | 2.2 | _   | μΑ    |

| I <sub>IZ</sub>  | Input Leakage Current  | _                    | -5  | _   | 5   | μΑ    |

| I <sub>OZ</sub>  | Output Leakage Current | _                    | -5  | _   | 5   | μΑ    |

Table 5-7: Electrical Characteristics for PLL  $V_{DD}$

| Symbol           | Parameter              | Condition            | Min | Тур | Max | Units |

|------------------|------------------------|----------------------|-----|-----|-----|-------|

| I <sub>DDS</sub> | Quiescent Current      | Quiescent Conditions | _   | 0.1 | _   | μΑ    |

| I <sub>IZ</sub>  | Input Leakage Current  | _                    | -5  | _   | 5   | μΑ    |

| l <sub>OZ</sub>  | Output Leakage Current | _                    | -5  | 1   | 5   | μΑ    |

# Chapter 6 A.C. Characteristics

#### Conditions:

IOVDD = 1.65V to 3.60V

$TA = -40^{\circ}C$  to  $85^{\circ}C$

Trise and Tfall for all inputs except Schmitt and CLKI must be < 50 ns (10%  $\sim 90\%$ )

Trise and Tfall for all Schmitt must be < 5 ms (10%  $\sim 90\%$ )

CL = 10pF (SDRCLK and SDRDAT[31:0])

CL = 15pF (All SDRAM signals except SDRCLK and SDRDAT[31:0])

CL = 30pF (HDB[15:0] and HRDY)

CL = 45pF (Gate Driver and Source Driver Interfaces)

CL = 15pF (Power Switches Control Interface)

CL = 30pF (GPIO Interface)

CL = 20pF (I2C Interface)

CL = 15pF (SPI Interface)

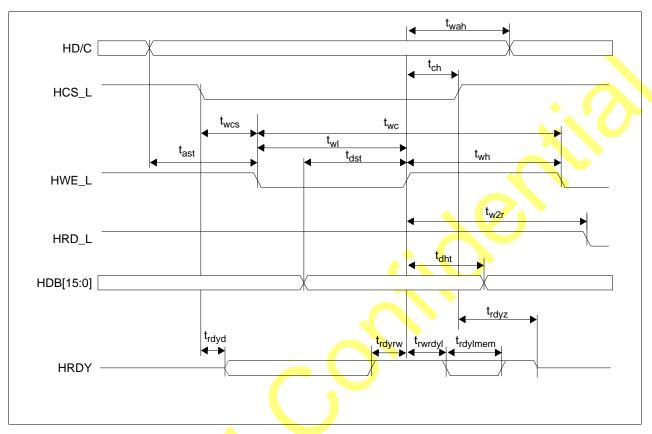

### 6.1 Clock Timing

### 6.1.1 Input Clocks

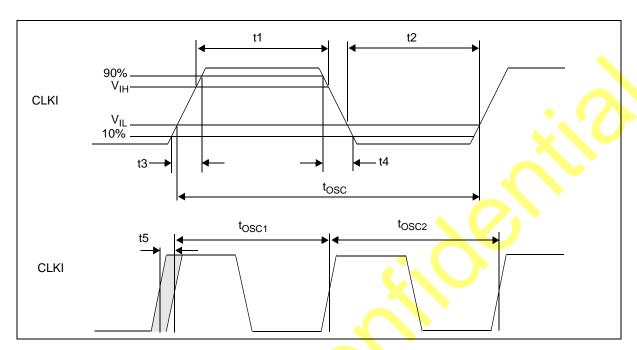

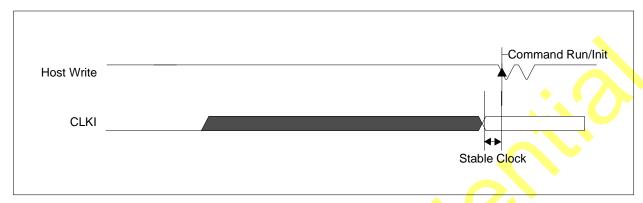

Figure 6-1 Clock Input Requirements (CLKI)

Table 6-1 Clock Input Requirements

| Symbol             | Parameter                                                                 | Min                 | Тур                | Max                 | Units |

|--------------------|---------------------------------------------------------------------------|---------------------|--------------------|---------------------|-------|

|                    | Input clock frequency of CLKI when PLL used for System Clock (see Note 1) | 20                  | _                  | 66.5                | MHz   |

| $f_{OSC}$          | Input clock frequency of CLKI when CLKI used for System Clock             | 0                   |                    | 133                 | MHz   |

|                    | Input clock frequency of OSC when PLL used for System Clock (see Note 1)  | 24                  | _                  | 27                  | MHz   |

| tosc               | Input clock peri <mark>o</mark> d                                         | _                   | 1/f <sub>OSC</sub> | _                   | μs    |

| t1                 | Input clock pulse width high (see Note 2)                                 | 0.4t <sub>OSC</sub> | _                  | 0.6t <sub>OSC</sub> | μs    |

| t2                 | Input clock pulse width low (see Note 2)                                  | 0.4t <sub>OSC</sub> | _                  | 0.6t <sub>OSC</sub> | μs    |

| t3                 | Input clock rise time (10% - 90%)                                         |                     | _                  | 500                 | ps    |

| t4                 | Input clock fall time (90% - 10%)                                         | _                   | _                  | 500                 | ps    |

| t5<br>(see Note 3) | Input clock cycle jitter (see Notes 4 and 5)                              | -150                |                    | 150                 | ps    |

- To achieve the maximum possible PLL output frequency, the input source frequency must be evenly divisible into 133 MHz. For further details on programming the PLL, see A.3.2, "Clock Configuration Registers" on page 166.

- 2. Input Duty cycle is not critical and can be 40/60.

- 3.  $t5 = t_{OSC1} t_{OSC2}$

- 4. The input clock cycle jitter is the difference in period between adjacent cycles.

- 5. The jitter characteristics must satisfy the t5 characteristics

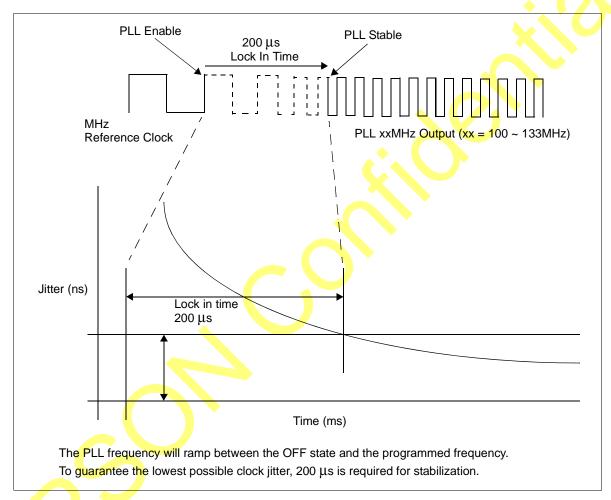

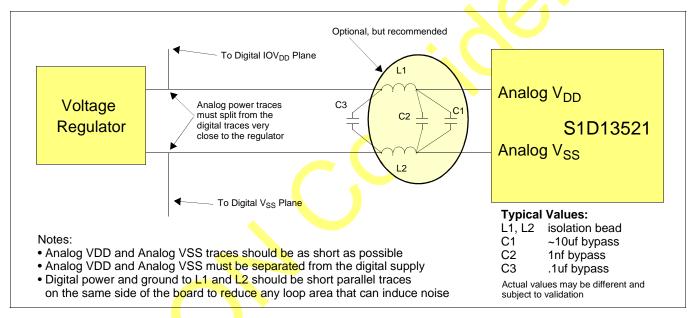

#### 6.1.2 PLL Clock

The PLL circuit is an analog circuit and is very sensitive to noise on the input clock waveform or the power supply. Noise on the clock or the supplied power may cause the operation of the PLL circuit to become unstable or increase the jitter.

Due to these noise constraints, it is highly recommended that the power supply traces or the power plane for the PLL be isolated from those of other power supplies. Filtering should also be used to keep the power as clean as possible. The jitter of the input clock waveform should be as small as possible.

Figure 6-2: PLL Start-Up Time

Table 6-2: PLL Clock Requirements

| Symbol             | Parameter                      | Min | Max | Units |

|--------------------|--------------------------------|-----|-----|-------|

| f <sub>PLL</sub>   | PLL output clock frequency     | 100 | 133 | MHz   |

| t <sub>PJref</sub> | PLL output clock period jitter | -2  | 2   | %     |

| t <sub>PDuty</sub> | PLL output clock duty cycle    | 45  | 55  | %     |

| t <sub>PStal</sub> | PLL output stable time         |     | 200 | μs    |

## 6.2 Power Supply Sequence

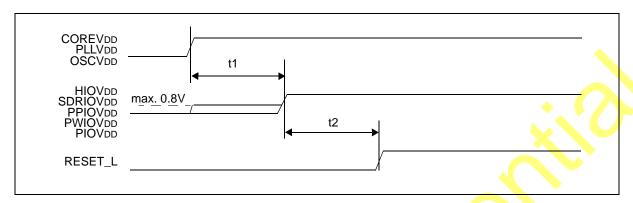

### 6.2.1 Power-On Sequence

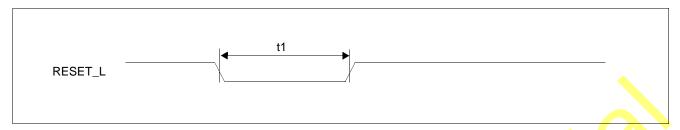

Figure 6-3: Power-On Sequence

Table 6-3: Power-On Sequence

| Symbol | Parameter                                                                           | Min    | Max | Units |

|--------|-------------------------------------------------------------------------------------|--------|-----|-------|

| T T    | HIOVDD, SDRIOVDD, PPIOVDD, PWIOVDD, PIOVDD on delay from COREVDD, PLLVDD, OSCVDD on | 0      | 500 | ms    |

| 1 17   | RESET_L deasserted from HIOVDD, SDRIOVDD, PPIOVDD, PWIOVDD, PIOVDD on               | Note 1 | _   | ns    |

1. For RESET\_L timing details, refer to 6.3, "RESET\_L Timing" on page 33.